英语原文共 5 页,剩余内容已隐藏,支付完成后下载完整资料

基于FPGA的多波形信号发生器*

张福江 王小飞 李东 邵海明

(中国计量学院电磁研究所,北京100013)

摘要:本文介绍了一种采用DDS(直接数字合成)和FPGA的多波形信号发生器的设计方案。 采用单片机控制FPGA产生波形数字信号,并结合D/A转换器和低通滤波器输出相位,幅度和频率分别可调,易于控制的波形。该系统具有宽广稳定的频率范围,高速响应性和高幅度调节分辨率。

关键词:DDS; 信号发生器; FPGA;单片机

1 介绍

DDS技术由于科学技术的提高而迅速发展并得到广泛应用,其原理是利用数控振荡器产生频率和相位可变的波形,由时钟,相位累加器和波形查表组成。D/A转换器和信号调理电路可构成多波形发生器.FPGA具有设计灵活,可靠性高,开发周期短,工作速度快等优点,因此被广泛应用于现代电子设备中。本文介绍了一种以FPGA为核心器件,采DDS技术的相位,幅度和频率分别可调的信号发生器,可输出正弦波,方波,三角波和锯齿波。系统具有频率范围宽,精度高,稳定性好并且很容易升级。

2 硬件设计

图1是整个框图。其工作原理如下:单片机通过将相位和频率控制字输入到FPGA中来生成一定的时序以控制FPGA。然后FPGA生成相应的相位和频率数字信号,模拟梯形信号。这些信号可以通过低通滤波器转换成所需的平滑信号。信号的幅度可以由控制DIA转换器的单片机来调整。 最后,在LED屏幕上显示波形,相位和频率。

图1.系统整体框图

2.1 DDS电路

DDS技术已经成熟并得到了广泛的应用,它利用数字技术产生信号波形,并基于采样定理。波形数据首先存储在存储器中,然后读取数字信号,通过数字信号转换为模拟阶梯信号DIA转换器。最后,需要的信号可以通过LPF得到.DDS具有信号频率稳定,全数字化,易于控制,超越连续相等优点。因此选择DDS作为研究对象。

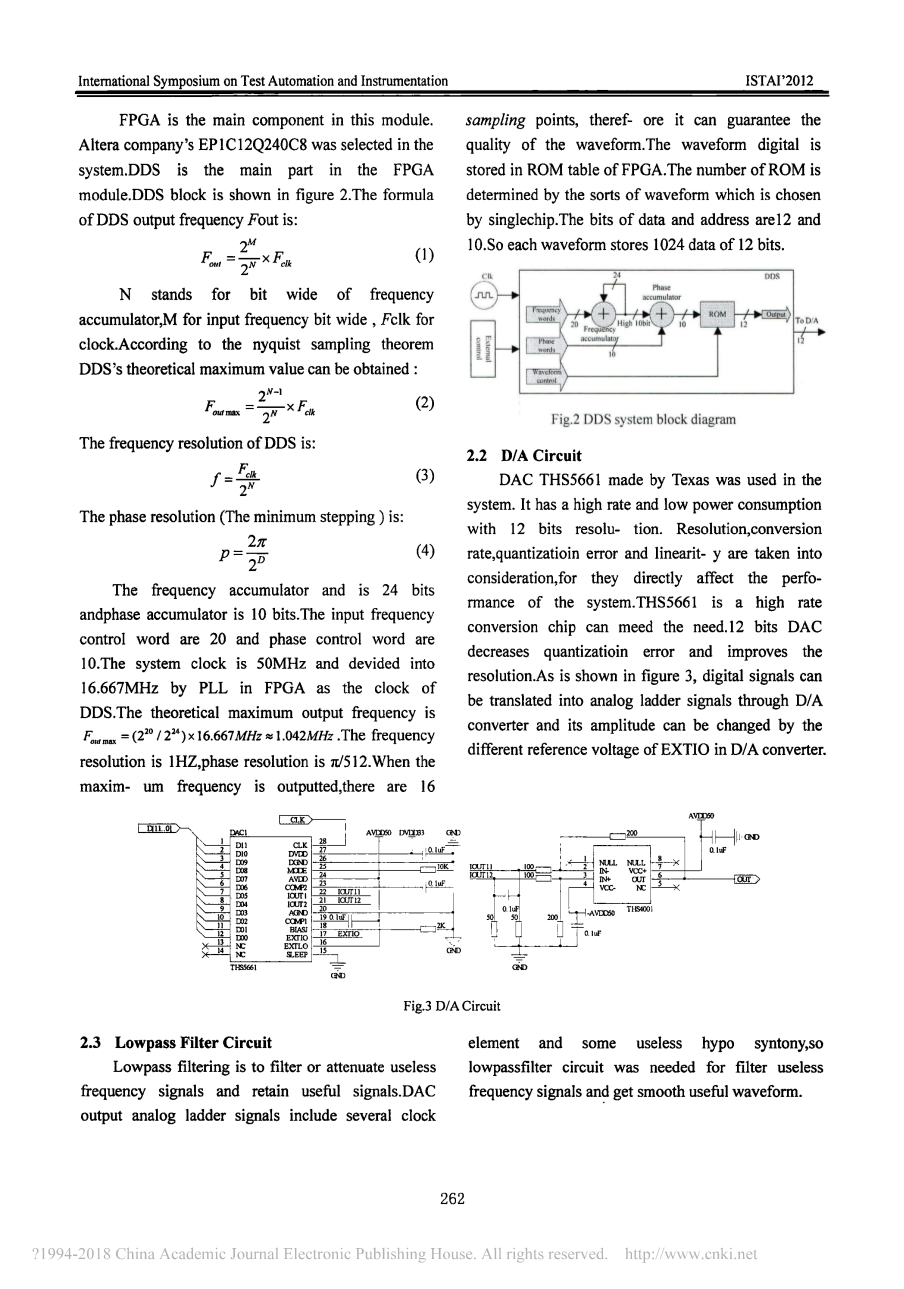

FPGA是该模块的主要组件。 在系统中选择了Altera公司的EP1Cl2Q240C8 .DDS是FPGA模块的主要部分.DDS模块如图2所示。公式的DDS输出频率Fout为:

。N代表频率累加器的位宽,M代表输入频率位宽,Fclk代表时钟。根据nyquist采样定理,可得到DDS的理论最大值:,DDS的分辨率是:,相位分辨率(最小增量)为。

频率累加器为24位,相位累加器为10位,输入频率控制字为20,相位控制字为1O,系统时钟为50MHz,并通过FPGA中的PLL分频为16.667MHz,作为DDS的时钟。理论最大输出频率是 =(220/ 224)times;16.667MHz asymp;1.042MHz。频率分辨率为1HZ,相位分辨率为pi;/512。当最大频率输出时,有16点,保证波形的质量。波形数字存储在 FPGA的ROM表中,ROM的数量由单片机选择的波形种类确定,数据和地址的位数分别为12和10,因此每个波形存储了1024位12位数据。

图2.DDS系统框图

2.2 D/A电路

系统中使用德克萨斯州生产的DAC THS566 l。它具有12位分辨率的高速率和低功耗。分辨率,转换率,量化误差和线性度都被纳入考虑,因为他们直接影响系统的稳定性.THS5661是一款高速率转换芯片,可满足需要12位DAC降低量化误差,提高分辨率。如图3所示,数字信号可通过DIA转换器转换为模拟梯形信号,其幅值可以通过DIA转换器中EXTIO的不同参考电压来改变。

图3.D/A电路

2.3低通滤波器电路

低通滤波器电路元件和一些无用的低谐振器,所以需要低通滤波。低通滤波是滤除或衰减无用频率信号并保留滤波器电路来滤除无用的频率信号并获得平滑的有用信号.DAC输出模拟梯形信号包括几个时钟波形。

2.4 键盘和显示电路

在系统中,用户需要输入和选择信号索引,因此应该有键盘和显示电路。系统采用4X4键盘和LCD12864显示器。通过扫描单片机控制的键盘,可以将某些命令和数据信号传递给FPGA将产生所需的波形信号,同时处理后的信号将显示在LCD128641上。系统操作简单,界面友好。

3.软件设计

本系统主要使用的开发语言是VHDL,开发平台是Quartus II 6.0.FPGA在Quartus II中编程和仿真并以VHDL语言设计。最后编译和仿真。系统的程序流程图如图4所示。

图4.流程图

基于FPGA的DDS设计

DDS大致可以通过设计频率累加器,相位累加器和ROM来实现在FPGA.ROM查找表中查找表可以通过Quartus II 6.0进行定制,最终创建ROM查找表即10位地址输入和12位数据输出。频率累加器和相位累加器的设计基于VHDL语言。

部分软件如下:

ENTITY DDFSCore IS GENERIC

( freq_words_width:integer:= 20;

-频率字的位宽度

phase_words_width:integer:= 10;

-相位字的位宽

freq_adder_width:integer: = 24;

-累加器的位宽度

phase_adder_width:integer:= 1O;

-相位累加器的位宽

lut_add_width:integer:= 10;

--LUT地址宽度

lut_dat_width:integer:= 12

--LUT数据宽度);

-频率累加器IF(CLKEVENT AND CLK =I) Then

reg_G_FreqWordslt;= FREQ_WORDS;

-同步频率字输入

reg_G_PhaseWords lt;= PHASE_WORDS;

-同步相位频率字输入

arith_G_FreqAcclt;= arith_G_FreqAcc reg_G_FreqWords;

end if;

- 相位累加器

arith G PhaseAcc lt;=arith_G_FreqAcc

(freq_adder_width-1 DOWNTO freq_adder_width-phase_words_width) reg_G_PhaseWords;

- 获取累加器的高位到LUT

reg_G_LUTAddress lt;= arith_G_PhaseAcc(phase_adder_width- 1 DOWNTO phase_adder_width - Jut_add_width);

DDFSOUT lt;= reg_G_OutRegister; --DFS 输出

如图5所示.ROM_COMPONENT是Five ROM查询表的头号文件,Add0是频率累加器,而Addl是相位累加器。

图5.DDS电路

3.2仿真

这部分主要是对FPGA系统的仿真。完成计算后,模拟功能和计时,然后可以知道设计结果是否符合原设计的要求。模拟时序如图6所示。

图6.仿真时序图

从仿真可以看出,在输出控制字之前,系统是高阻抗。控制字的输入可以分为两步:控制字的输入和控制命令的输入,当ALE设置为高电压时,控制命令输入; WR为高电平,控制字。控制命令由表1所示。通过P0和波形选择P1输入频率和相位字。

以图6为例,ALE和WR产生一定的时序来控制P1 和P2输入数据,6082H是9〜16位的使能输入---频率控制字中间8位 - 频率控制字。1OH频率控制字,即频率控制字输入为1OOOH,由式(1)可知, Fau1 =()times;16.667MHzasymp;8.138k.Hz。6042H控制使能波形选择。首先ROM数据,也就是说,DDFSOUT输出是第一个ROM数据,输出约为8kHz。

4 系统测试

键盘输入一定指标的波形信号,如波形选择,频率输入相位输入和单片机幅度。 单片机进行产生当前时间序列,输入波形索引进入FPGA和DAC并生成需要的波形信号。输出信号指数用示波器测量,并与输入信号进行比较,分析波形效应和误差。因为相位、幅度和频率都是由软件控制的。系统存在误差,因此误差得到补偿。经过多次测试获得以下指标:

在系统错误,因此错误得到补偿。经过多次测试,获得以下指标:

◆ 输出频率:1HZ-1MHz

◆ 输出电压:0-plusmn;SV

◆ 频率分辨率:1HZ

◆ 相位分辨率:pi; / 512

◆ 电压分辨率:12 bit

◆ 输出波形:正弦,方形,三角形以及锯齿波并能通过更改存储列表ROM生成其他波形。

|

控制命令 PIP0(H) |

功能 |

|

6080

|

。频率控制字低8位输入启用 |

|

6082 |

频率控制字中间8位输入 |

|

6084

|

启用 频率控制字高8位输入启用 |

|

6090 |

相位控制字低8位输入使能 |

|

6092 |

相位控制字高2位·输入使能 |

|

6042

|

波形选择控制字输入启用 |

表1

5 结论

本文介绍a设计的a基于FPGA的多波形发生器和DDS。相位,幅度和频率可以是调整和相当理想的正弦,方形,三角形和锯齿波可以生产。系统有宽频率范围,稳定的频率范围,高速响应性和高振幅调节分辨率。该系统操作简单,易于控制,可以在学习和实验中取得良好的效果。

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[21997],资料为PDF文档或Word文档,PDF文档可免费转换为Word

您可能感兴趣的文章

- 饮用水微生物群:一个全面的时空研究,以监测巴黎供水系统的水质外文翻译资料

- 步进电机控制和摩擦模型对复杂机械系统精确定位的影响外文翻译资料

- 具有温湿度控制的开式阴极PEM燃料电池性能的提升外文翻译资料

- 警报定时系统对驾驶员行为的影响:调查驾驶员信任的差异以及根据警报定时对警报的响应外文翻译资料

- 门禁系统的零知识认证解决方案外文翻译资料

- 车辆废气及室外环境中悬浮微粒中有机磷的含量—-个案研究外文翻译资料

- ZigBee协议对城市风力涡轮机的无线监控: 支持应用软件和传感器模块外文翻译资料

- ZigBee系统在医疗保健中提供位置信息和传感器数据传输的方案外文翻译资料

- 基于PLC的模糊控制器在污水处理系统中的应用外文翻译资料

- 光伏并联最大功率点跟踪系统独立应用程序外文翻译资料