英语原文共 6 页,剩余内容已隐藏,支付完成后下载完整资料

用FPGA嵌入式软处理器实现访问SD卡的四位数据传输

摘 要

安全数字(SD)卡具有可移动、非易失性和闪存的性质,在基于FPGA的系统中作为二级存储使用时非常受欢迎。目前,大多数FPGA开发者由于4位串行设计的复杂性,更喜欢用1位SD模式的数据传输作为访问SD卡的手段。因此,速度会受到很大影响。本文讨论了4位SD模式数据传输的固件的设计和实现。一个基于开关、按钮、存储器和SD卡接口的简单硬件应用被用来说明拟议的固件的功能,特别是为数据访问生成所需的控制信号。同时,Verilog HDL被用于硬件设计,而软件控制则用C语言编码。该系统在Altera DE-4板上实现,该板带有FPGA Stratix IV GX EP4SGX230和32位NIOS-II嵌入式软处理器。在数据吞吐量方面,新的固件在访问单个数据块时,与标准的1位日期传输相比要快80%。

关键词:4位/1位标清模式; FPGA;NIOS‑II处理器;Altera DE-4板; Stratix IV

Implementation of 4-Bit Data Transmission for Accessing SD Card with FPGA Embedded Soft Processor

Abstract

Secure Digital (SD) cards being removable, non-volatile and flash memory in nature, are highly preferred for use in FPGA based systems as secondary storage. Currently most FPGA developers prefer 1-bit SD mode data transmission as a mean to access the SD card due to the complexity of 4-bit serial design. Hence, the speed is significantly compromised. This paper discusses the design and implementation of a firmware for 4-bit SD mode data transmission. A simple hardware application based on switches, buttons, memory and SD card interface is used to illustrate the functionality of proposed firmware, particularly the generation of the required control signal for data access. Meanwhile the Verilog HDL is used for hardware design while the software control is coded in C language. The system is implemented on Altera DE-4 board with FPGA Stratix IV GX EP4SGX230 and 32-bit NIOS-II embedded soft processor. In terms of data throughput the new firmware is 80 % much faster compared to a standard 1-bit data transmission when accessing a single block of data.

Keywords : 4-bit/1-bit SD mode; FPGA; NIOS-II processor; Altera DE-4 board; Stratix IV.

- 简介

现场可编程门阵列(FPGA)由于其可重构性[1][2]、高计算能力[3]、支持实时处理[4]和并行性[2][3][4],正日益被纳入ASIC和SOC设计中。像任何处理单元一样,FPGA也依赖于存储器系统,它可能只是短期主存储器或可选的长期辅助存储器。目前,供应商的FPGA或开发板提供的片上或板上存储器通常尺寸较小,因此,对于依赖高计算能力和并行性的设计来说,其灵活性较小,同时需要更大的空间来存储其次要性质的数据。因此,硬件设计者在实际考虑设计和实现数据密集型系统之前,总是要考虑到二级存储器及其可用的尺寸。这些系统可能包括高清(HD)图像和视频处理系统、语音识别和处理系统、基于ANN(人工神经网络)的学习系统、医疗成像系统等等。

SD卡是可移动的、非易失性的、抗震的基于闪存的存储设备,由于其尺寸较小、功耗较低、成本较低,因此被作为二级存储而受到青睐[5][6][7]。与笨重的机械硬盘相比,它们支持多种写入特性并易于处理[7][8]。现在SD卡在小型消费设备中非常流行,如PDA、数码相机、手提电话和其他便携式设备[9]。同样,基于FPGA的系统经常使用SD卡进行长期存 储,因为它们的原生或片上和板上存储器显然尺寸非常小,而且大多具有易失性。像其他任何存储类型一样,SD卡也使用文件系统,负责组织其上的文件和文件夹。2GB或以下的SD卡使用文件分配表(FAT)FAT-12或FAT-16作为文件系统,4GB或以上的SD卡通常使用FAT-32文件系统[10]。目前,FPGA板上的SD卡接口除了默认的1位SD和SPI模式(只允许SD命令的一个子集)外,已经有4位设计升级的选项。即使如此,大多数FPGA设计者还是倾向于坚持使用1位SD模式,因为为4位数据传输设计一个固件很困难。

这种困难主要来自于以较高频率传输时复杂的时序结构,以及设计一个强制性的16位纠错[10]。本文提出了一个基于4 位读/写模式的固件,用于利用SD卡作为二级存储。为了分析和比较了解SD模式下的数据传输,实现了1位的SD模式。

本文的组织结构如下。第2节讨论了硬件设计,第3节解释了SD卡的基本原理。第4节介绍了读写操作,然后在第5节介绍了SD 4位和1位模式的读写操作的软件实现。第6节介绍了实验结果和讨论,最后在第7节得出结论。

- 系统硬件

这项开发工作主要是基于嵌入式32位NIOS-II FPGA软处理器,由一些基本的并行输入/输出(PIO)、DDR2(双数据率) RAM和片上存储器组成。具体来说,该系统使用的是SD卡接口,而且它还提供了50MHz的系统时钟和复位接口。该系统可以通过按下一个按钮在SD卡上读取或写入数据。DDR2 也可以用类似的方式进行读取或写入。在这里,DDR2只是 作为实时数据存储的原型提供给以后要实现的任何系统。最初由任何传感器、高清摄像机等产生的实时数据可以存储在DDR2上,然后也可以存储在SD卡上以便长期使用。这个系 统带有内置软件,可以选择DDR2、SD卡或临时程序变量作为数据源。同样地,这些来源中的任何一个都可以专门作为数据的目的地。换句话说,这个系统在SD卡、DDR2和程序变量之间建立了一个简单的数据接口。

2.1系统规格

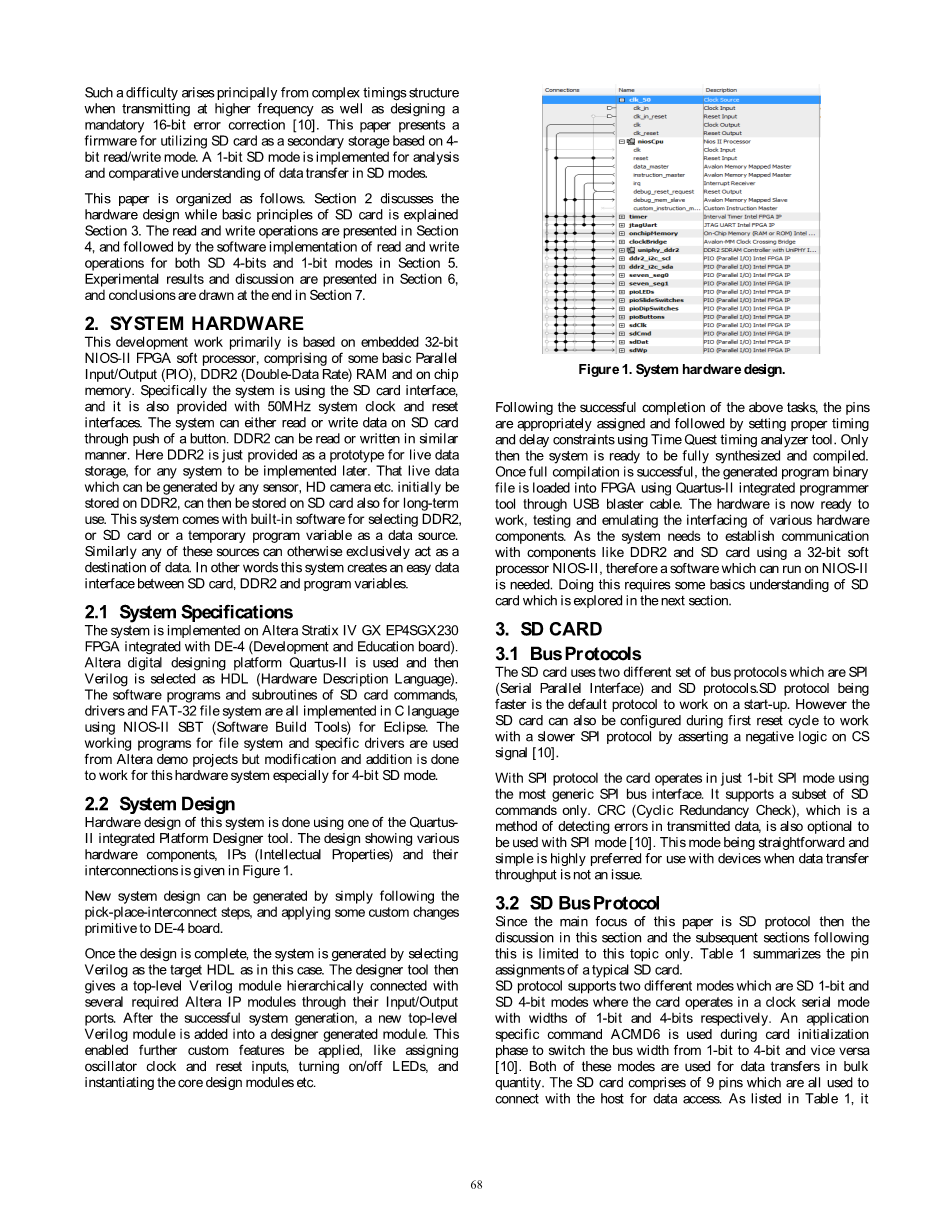

该系统的硬件设计是使用Quartus- II集成平台设计工具之一完成的。图1给出了显示各种硬件组件、IP(知识产权)及其互连的设计。

新的系统设计可以通过简单地按照拾取-放置-连接的步骤生成,并将一些定制的变化原始地应用于DE-4板。

一旦设计完成,通过选择Verilog作为目标HDL来生成系统, 就像本案例中一样。然后设计者工具给出一个顶层的Verilog 模块,通过其输入/输出端口与几个所需的Altera IP模块分层连接。 在成功的系统生成后,一个新的顶层Verilog模块被添加到设计器生成的模块中。这使得进一步的定制功能得以应用,如分配振荡器时钟和复位输入,打开/关闭LED,以及实例化核心设计模块等。

图1.系统硬件设计

2.2系统设计

该系统的硬件设计是使用Quartus- II集成平台设计工具之一完成的。图1给出了显示各种硬件组件、IP(知识产权)及其 互连的设计。

新的系统设计可以通过简单地按照拾取-放置-连接的步骤生成,并将一些定制的变化原始地应用于DE-4板。

一旦设计完成,通过选择Verilog作为目标HDL来生成系统, 就像本案例中一样。然后设计者工具给出一个顶层的Verilog 模块,通过其输入/输出端口与几个所需的Altera IP模块分层连接。 在成功的系统生成后,一个新的顶层Verilog模块被添加到设计器生成的模块中。这使得进一步的定制功能得以应用,如分配振荡器时钟和复位输入,打开/关闭LED,以 及实例化核心设计模块等。

在成功完成上述任务后,将对引脚进行适当的分配,然后使用Time Quest定时分析器工具设置适当的定时和延迟约束。只有这样,系统才准备好进行完全综合和编译。一旦完全 编译成功,使用Quartus-II集成编程器工具通过USB防爆电缆将生成的程序二进制文件加载到FPGA。现在硬件已经准备好工作,测试和模拟各种硬件组件的接口。由于该系统需要使用32位软处理器NIOS-II与DDR2和SD卡等组件建立通信,因此需要一个可以在NIOS-II上运行的软件。做到这一点需要对SD卡有一些基本的了解,这将在下一节进行探讨。

- SD卡

3.1总线协议

SD卡使用两套不同的总线协议,即SPI(串行并行接口)和SD协议。SD协议更快,是启动时的默认协议。然而,SD卡也可以在第一次复位周期中通过对CS信号施加负逻辑来配置为使用较慢的SPI协议[10]。

通过SPI协议,该卡仅在1位SPI模式下使用最通用的SPI总线接口运行。它只支持SD命令的一个子集。CRC(循环冗余检查)是一种检测传输数据错误的方法,也可以选择与SPI 模式一起使用[10]。这种模式简单明了,当数据传输的吞吐量不是问题时,它是设备使用的首选。

3.2 SD总线协议

由于本文的主要重点是SD协议,那么本节和后面的章节的讨论就只限于这个主题了。表1总结了一个典型的SD卡的引脚分配。

SD协议支持两种不同的模式,即SD 1位和SD 4位模式,卡在时钟串行模式下运行,宽度分别为1位和4位。 在卡的初始化阶段,一个特定的应用命令ACMD6被用来将总线宽度从1位切换到4位,反之亦然[10]。 这两种模式都是用于大量的数据传输。SD卡由9个引脚组成,全部用于与主机连接以获取数据。正如表1中所列,它包括4个双向数据引脚,3个电源引脚,1个时钟线和1个双向命令线,用于发送命令和接收卡的响应。

表1.SD卡引脚说明

SD 1位模式只使用DAT0进行双向数据传输。相反,SD 4位模式使用所有四条数据线,即DAT0-DAT3用于相同的目的。由于这个原因,4位模式有望比1位模式的工作速度快得多,几乎是4倍[11]。

3.3 SD数据包格式

图2.sd协议的数据包格式

在读或写或状态或响应操作中,数据传输是以块为单位进行的。大多数高容量SD卡(SDHC)的块大小通常为512字节。在本系统中实现的软件也使用512字节作为数据读写操作的块大小。在SD模式下,有两种类型的SD卡数据包格式。它们是(i)字节宽度和(ii)宽幅数据格式,如图2所示。

从最不重要的字节开始,在字节宽度的数据格式中,各个位被转移为最重要的位在前,最不重要的位在后。而在宽幅数据格式中,整个数据从最有意义的位开始移位。在这两种情况下,每次传输都必须以0为起始位,1为结束位。在4位SD模式下,所有单独的DAT线将携带128个字节,总和为一个512字节的块,如图2所示。

与SPI不同,两种SD模式都依赖16位CRC错误保护来进行数据传输。在SD 1位模式下,DAT0上的数据必须在传输结束位之前加上2字节的CRC码。在4位SD模式下,所有DAT0-DAT3线在所有DAT线的传输结束位之前也必须有2字节的CRC码作为后缀。而在第二种情况下,必须对所有DAT线分别计算和测试16位CRC码[10]。

3.4 SD命令格式

控制信号或SD命令需要控制和给SD卡提供任何所需功能的指示。这里的CMD线用于发布命令,也用于接收响应,作为对SD模式下发布的命令的反馈。命令集中的所有命令都以6个字节的打包帧形式出现,其具体格式结构如图3所示。如果是命令,传输位为1,反馈响应为0。一个6位的唯一的命令号指示卡要做什么,一个可选的32位参数定义了必要的参数。在这种情况下,CRC7是一个7位的CRC码,用于命令完整性验证。

图3.SD命令帧结构

由于6位被保留给命令索引,因此SD卡可以

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[591476],资料为PDF文档或Word文档,PDF文档可免费转换为Word

您可能感兴趣的文章

- 饮用水微生物群:一个全面的时空研究,以监测巴黎供水系统的水质外文翻译资料

- 步进电机控制和摩擦模型对复杂机械系统精确定位的影响外文翻译资料

- 具有温湿度控制的开式阴极PEM燃料电池性能的提升外文翻译资料

- 警报定时系统对驾驶员行为的影响:调查驾驶员信任的差异以及根据警报定时对警报的响应外文翻译资料

- 门禁系统的零知识认证解决方案外文翻译资料

- 车辆废气及室外环境中悬浮微粒中有机磷的含量—-个案研究外文翻译资料

- ZigBee协议对城市风力涡轮机的无线监控: 支持应用软件和传感器模块外文翻译资料

- ZigBee系统在医疗保健中提供位置信息和传感器数据传输的方案外文翻译资料

- 基于PLC的模糊控制器在污水处理系统中的应用外文翻译资料

- 光伏并联最大功率点跟踪系统独立应用程序外文翻译资料