英语原文共 7 页,剩余内容已隐藏,支付完成后下载完整资料

用于双头PET探测器的基于FPGA的全数字化数据采集系统

摘要:我们提出了一种全新的全数字化的、灵活且高效的数据采集系统,该数据采集系统适用于双头正电子发射计算机断层显像扫描仪,用于小动物成像应用。本系统使用一个自由运行的、采样率达到65MHZ的12位八通道模数转换器,用于将探测器检测到的信号进行转化成数字信号。转化后的数字信号会传输到FPGA芯片 Spartan 6内部,用于结果处理。最后利用Xilinx的嵌入式开发工具包(EDK)和主处理器搭建起一个嵌入式系统进行数据的采集。为了获得比ADC采样周期更长的时间分辨率,而无需外部设备来混合信号,该FPGA中采用了恒定系数鉴别器(CFD)的数字化版本的方法。使用FPGA获取的信息包括:过程的时序、能量鉴别与判断、位置测定与多信号同步处理。可能的多信号同步处理的在线处理会显著的减少传输到电脑端的数据量,多信号同步过程会暂时先写在开发板提供的一个外部存储器中,然后通过以太网接口传输到PC端,用于图像再现。数据的最小后置处理需要优先于重建过程,一个小的探测器对包含一个BGO阵列,再组合一个位置敏感型光电倍增管(PSPMT)用于读出系统的评估。采集获取的结果证明所提出的结构框架能够用于双头PET探测器的读取,来用于小动物成像应用。

关键字: BGO;DAQ;数字化恒定系数鉴别器(dCFD);FPGA;PSPMT;PET;Spartan 6

1 介绍

临床前的小动物图像不仅在疾病与非疾病的生物学研究领域扮演着重要的角色,在药物设计与评估方面的重要性也举足轻重。PET技术和其他一些高灵敏性的图像形态,比如与针对不同的生物化学指标分析的异常放射性标记的特定分子所结合的单光子发射体层成像(SPECT)已经推动原子核医药学进入了一个新的图像领域。而众所周知,由于电子瞄准的原因,与SPECT相比,PET提供了更高的灵敏度和空间分辨率。正是因为这个原因,PET现在在不管在动物还是人类的生理成像过程中都是一个艺术手法的状态。这是作为放射性分配被无损耗的完成。体内的正电子发射型发射型药物会被周围的检测器所监控。通过使用数学算法,跟踪器的分配会被重构到一个断层图像,该断层图像能提供放射性药物的浓度。

在过去的二十年间,许许多多的实验小组发现研制了非常灵敏的、高分辨率的小动物PET系统,通过使用专门用于此意图所设计的微小、高分辨率的PET扫描仪,小动物PET系统能够捕捉到比如老鼠和猫的图像。这些系统中的其中有些已经进行了商业化,并且已经在临床前的潜伏期调查中广泛使用了。小动物PET扫描仪探测器的几何形状各不相同,有些设计使用致密块状探测器模块,而其他设计会使用更少但更大的平板探测器组件。大多数小动物PET扫描仪是全环设计,形成长圆筒的几何形状。配置时要求使用数以百计的检测器模块,且该检测器模块由数以万计的水晶元素组成。这使得该扫描仪的成本十分昂贵。在另一方面,一些模型采用带有旋转支架或者旋转动物床的部分环或者双头几何体。以降低计数值的灵敏度为代价来减少生产成本。此外,在台式的基础上,基于2个5times;10的BGO闪烁体探测器和H8500 PSPMTs的两平面头系统,现在已经能够商业化,并且最近已经升级成为四平面头。

平面PET头在过去的十年间广泛应用的另一个应用领域就是正电子发射乳腺照相术(PEM),在该领域里,一些基于该相对平板式检测器的系统的概念已经作为技术原型和临床验证系统被提出,最终,一个最近的对于该类型系统的挑战性的应用正在图像培养中。因此,除了完整环的PET系统,大多数单面头处理所关心的是持续的,尤其是对于那些扫描仪的总花费需要压低的应用。

几乎所有的使用闪烁检测器的应用都需要确定存放在闪烁器内的能量,这个数值通常在光检测器的脉冲输出进行积分之后所得到。利用这个方法,时间的时序信息丢失,使得有必要使用额外的硬件来导出它。习惯上来说,小动物PET扫描仪的前端电子包含有许多离散的部件,而这些零散的部件执行必要的数据采集步骤和脉冲处理功能。由于可编程逻辑器件在密度方面已经有所成长,所以现在需要更多地投入来将FPGA引进到数据采集这一步,使采集系统成为紧凑、低成本且灵活的系统。

经典的前端模拟电子器件正在被基于基于高速自由运行的ADC所取代,同时数字信号处理过程发生在FPGA内部。对于小动物PET系统定时拾取通常依赖于外部恒定分数鉴别器(CFD)或类似的电路,一些小组利用FPGA内部额外的数字处理来取代外部的电路。这种架构增加了读出系统的灵活性和可扩展性,相比于到目前为止基于总线系统适用的核仪器仪表模块(NIM),欧罗巴电磁阀模块(VME)总线和计算机自动测量与控制,它提供了一种更低成本的途径。

在本设计中,我们提出来了一种新的、全数字化的、灵活且高效的数据采集系统,该系统适用于双端头PET探测器, 该探测器主要应用在小动物的成像应用中。目标实现的系统所基于的是一个低成本、通用的FPGA开发工具包和低成本自由运行的ADC,一个BGO-PSPMT 探测器对被用来评估此读出系统,所有需要的信息比如能量计算、位置测算、时序计算都能够从来自FPGA内部的数字化前置放大信号探测器。为了达到让时间分辨率比采样周期更高的目的,需要实施恒定馏分鉴别(CFD)算法的一个数字版本,基于精确时间戳潜在同步事件的在线硬件处理,大大减少了用于传输至计算机的数据的规模和需要进行的额外的后处理。根据现在已有的知识,类似的用于双头PET探测器的低成本实现方式在文学中并不存在,并且所提出的数据采集系统在这样的一个应用中,有潜在的作为一个简单的、低成本的读出的解决方案。

本文的整个结构可以分为三个部分,在第一部分里,为了评估DAQ的架构,对整体的系统结构,采集方法和实验的执行进行了详细的描述;在第二部分,关于空间,能量和时间分辨率以及计数率性能的测量值结果,这项工作带着结论和正在进行的工作关闭。

2 材料和方法

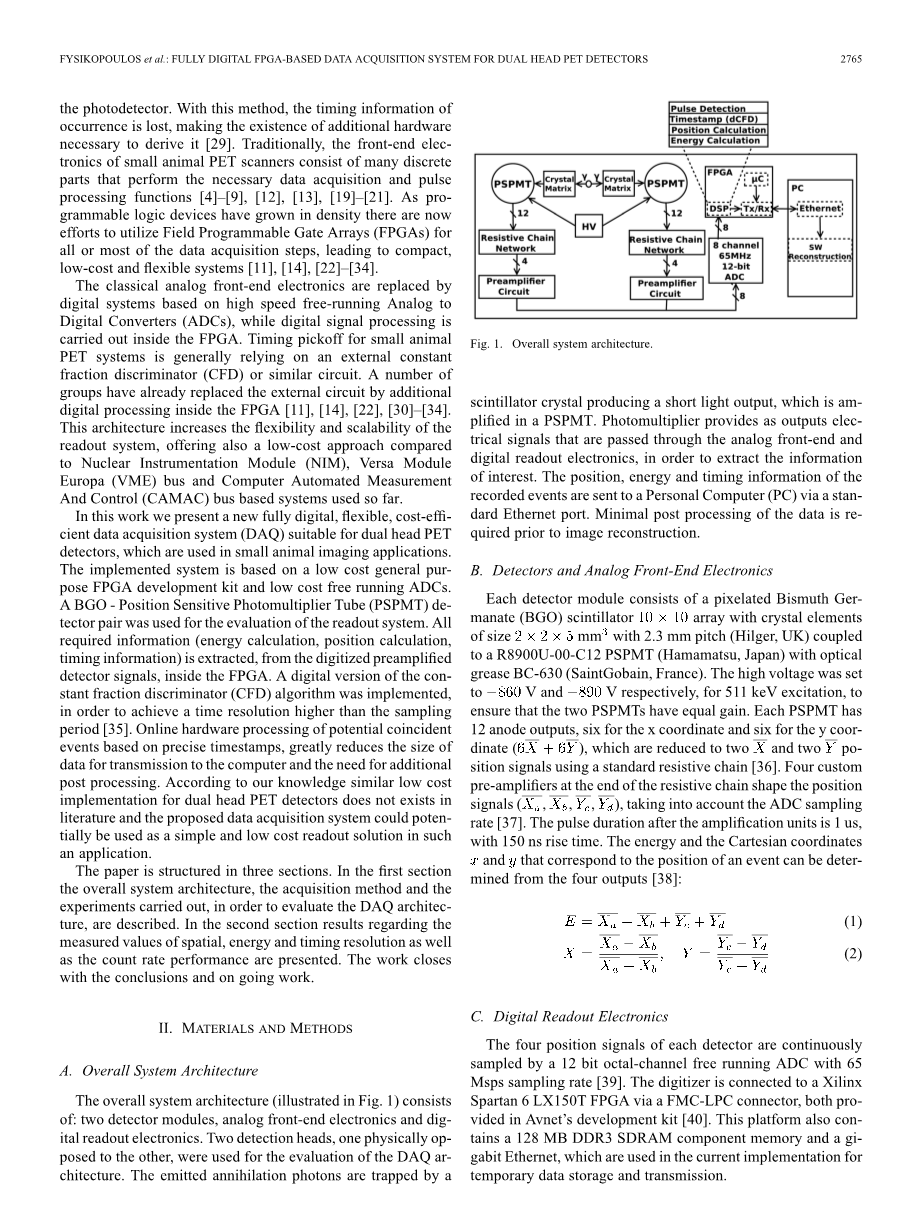

- 系统整体构架

系统整体构架(如插图1所示)主要包含:2个探测器模块,模拟前端电子器件和数字读出电子器件,2个探测头,一个物理上对其他的对抗,用于对DAQ体系结构的评估。所发射的湮灭光子被困在了一个闪烁体晶体来制造一个短的光输出。该输出是在PSPMT中进行扩增的。光电倍增管作为输出的电信号通过模拟前端和数字读出电子,来提取有利的信息。记录的事件的位置、能量、和时间信息经由标准以太网接口发送到个人计算机。数据的最小化的后处理之前的图像重建是必需的。

B.探测器和模拟前端电子器件

每个探测器模块包含了一个像素化锗酸铋(BGO)的带有2.3mm间距的2times;2times;5尺寸的水晶元素闪烁体阵列,同时带有一个R8900U-00-C12 PSPMT(滨松,日本)与光学油脂BC-630(圣戈班,法国)。对于511keV的激励,高电压分别设置为-860V和-890V,来保证两个PSPMTs有平等的增益。每个PSPMTs有12个正极输出,分别是x坐标6个和y坐标6个(),使用一个标准的电阻链减少为2个x坐标和2个y坐标。在电阻链的末端的四个自定义的预放大器确定了位置信号,并考虑ADC的采样速率。扩增单位后的脉冲持续时间为1us,其中上升沿时间为150ns。能量和笛卡尔坐标和对应于时间的位置可以从四个输出来确定:

,

C.数字读出电子器件

每个探测器的四个位置信号需要不断进行采样,采样的ADC为12位的八通道自由运行,且采样速率为65MSPS。数字转换器通过FMC-LPC连接器连接到赛灵思Spartan6 LX150T FPGA,这两个都在安富利的开发套件提供。该平台还包含一个128 MB DDR3 SDRAM组件的内存和一个千兆以太网,该千兆网用于临时的数据存储和数据传输。

使用一个嵌入式系统用于采集,并使用赛灵思的嵌入式开发套件(EDK)和

Microblaze(uB),Microblaze(uB)为一个32位的RISC软处理器。系统时钟为66.67MHz。内部自定义的核采用VHDL硬件描述语言来描述采集数字化的数据的信号处理过程。核操作是使用Modelsim仿真工具和ChipScope Pro的调试工具。所有其他接口都通过赛灵思公司提供的IP内核控制。所实现的系统所用到的核主要由以下几种:

- 专用的数字信号处理(DSP)模块的应用;

- 用于通过JTAG在线调试的调试模块(MDM);

- 外部128MB内存控制器(MPMC)DDR3 SDRAM;

- 中断控制器(INTC);

- 以太网控制器(Soft TEMAC);

- 用于内部8kB存储的存储控制器;

- 定时器。

D.数字信号处理(DSP)模块

Spartan 6 输入的SerDes(ISERDES)块用于将FPGA内部的ADC数据进行反序列化,一个双时钟First In First Out (FIFO)被用于交换两个不同时钟域的数据:即ADC的时钟频域(65MHz)和系统时钟频域(66.67MHz),在该系统的时钟频率域中,反序列化的输出被连续地存储在八位在65MHZ的取样率移位寄存器,对于985毫微秒的持续时间。这种尺寸可确保扩增脉冲(1us的持续时间)完整存储在寄存器内。

当一个检测器(4输出信号之和)的瞬时能量超过一个预定的数字阈值,这意味着一个光子的到来,接下来有限状态机(FSM)就会被触发。为了确定该光子是否是在湮灭过程中产生的。有限状态机会打开一个60ns的时间窗口,以允许在相对的检测器的第二光子的检测的可能。如果第二个光子的能量超过对应的数字阈值,那么延迟电路将会被激活,进而使两个脉冲的其余样品移位至寄存器内。然后FSM将会整合脉冲,以及计算用于从所述探测器记录的每个事件的时间戳,否则该状态机等待时间窗就会等于被放大的脉冲的持续时间(985纳秒),并执行重新启动操作。在记录的数据正在接受处理的同时,第二组寄存器将会准备接收下一个潜在时间所发送的数据。因为扩增BGO脉冲的上升时间相对缓慢,只有150ns,所以需要对粗符合门的预设置为60ns,整体过程如图3所示。

恒定馏分鉴别(CFD)算法的一个数字版本将会被应用,以实现比采样周期更高的时间分辨率,dCFD通过从每个探测器取4个通道信号的总和,由一个恒定分数相乘,然后将其加到原始的已经进行反相并延迟的和信号。一旦最后一个正采样和第一个负采样被确定,过零时间就能通过线性内插确定。FSM跟踪采样间隔,在该间隔里,为每个探测器锁定零交叉。从而消除了为同步事件所需要对符合处理器或者后处理的需要。零交叉点提供了15位的分辨率的精度。

如果所计算的时间戳位于同一采样间隔内或内两个连续的采样间隔(对应于31ns巧合定时窗口),有关位置、能量、时序和许多零采样间隔的信息,将会通过由赛灵思的存储控制器(MPMC)提供的一种高性能端口——NPI方式写入到外部存储器,否则之前选定的随机事件将会被丢弃。传输数据速率内存为 2100 Mbps(128位写在四个系统时钟周期)。

E.数据传输

除了NPI是用于由DSP模块写入数据到内存中,在当前设计MPMC配置有两个端口,软直接内存访问(SDMA)端口用于通过一个locklink接口使用外部存储来连接以太网控制器。SDMA为流数据提供了高性能直接内存访问。为了访问数据和存储在DDR3内存里的程序,Xilinx CacheLink(XCL)端口被Microblaze嵌入式处理器所使用。处理器用于控制数字输出到PC之间的网口输出。

内存中每存储1000个事件,DSP模块就会发出一次中断信号,在DSP模块有两个中断过程对应于存储在内存中的1000个事件的奇数和偶数组。为了有并发访问的内存写(DSP模块)、阅读(Microblaze)过程,奇数和偶数组数据将被写入内存的不同部分(不同的起始地址)。Microblaze在每一个中断时,使用C语言编程来读取数据,并将他们传递给轻量级TCP / IP(LWIP)网络栈。该网络栈用于使用用户数据报协议(UDP),将数据发送到运行在Linux机器上服务器,使用一个计时器在每个恒定的时间间隔中断来发送udp数据包。LWIP是用于嵌入式处理器优化的tcp/ip协议栈优化,并且为高效数据流提供了一个有用的接口。通过这个配置,可以实现的最大数据传输速率是60 Mbps。

F.后处理

用C语言编程开发的定制软件将会用在能源调整窗口和图像重建中。使用价值预测焦平面断层扫描算法将符合的数据进行分组。250–650 keV的能量窗口用于所有的重建的图像中[34]。

G.系统性能

为了评估采集系统的结构,PET的性能参数将会用每隔50mm一个探测头并且反向对齐的装置进行测量。计数率的性能是通过一个圆柱管进行评估的,该圆柱管长35mm,直径为5mm,放置在离两个探测器头25mm距离的地方。最初的活性度为235uCi。的空间分辨率是由两个相对的平行检测器之间的平均平面步进一个长15毫米和1毫米的直径,填充毛细管源,在直线跨越水平方向,再重合图像取符合计数率轮廓来进行测量。对于时间分辨率的测量,一个点状FDG源会被放到视野区域的中心,重合时间之间的时间戳的区别将会被记录。为了测量重合定时窗口是如何影响重合数据速率,在同步事件进一步选择通过每次步进1ns从1ns到31ns的接受定时窗口后处理。系统的灵敏度通过再次放置点状FDG源在视野区域的中心来进行测量。真正的符合计数率和源排放之间的比率提供了在CFOV的预期绝对灵敏度的一个评估。为了确定能量分辨率,需要在探测器之前放置一个Ga泛流源。

您可能感兴趣的文章

- 饮用水微生物群:一个全面的时空研究,以监测巴黎供水系统的水质外文翻译资料

- 步进电机控制和摩擦模型对复杂机械系统精确定位的影响外文翻译资料

- 具有温湿度控制的开式阴极PEM燃料电池性能的提升外文翻译资料

- 警报定时系统对驾驶员行为的影响:调查驾驶员信任的差异以及根据警报定时对警报的响应外文翻译资料

- 门禁系统的零知识认证解决方案外文翻译资料

- 车辆废气及室外环境中悬浮微粒中有机磷的含量—-个案研究外文翻译资料

- ZigBee协议对城市风力涡轮机的无线监控: 支持应用软件和传感器模块外文翻译资料

- ZigBee系统在医疗保健中提供位置信息和传感器数据传输的方案外文翻译资料

- 基于PLC的模糊控制器在污水处理系统中的应用外文翻译资料

- 光伏并联最大功率点跟踪系统独立应用程序外文翻译资料