英语原文共 12 页,剩余内容已隐藏,支付完成后下载完整资料

循环:管道适应容忍过程变化

摘要:

过程变化会影响处理器管道,使一些阶段变慢,其他阶段更快,从而加剧管道不平衡

这降低了管道可达到的频率

为了提高性能,本文提出了ReCycle,

一个将循环时间窃取全面应用于管道的架构框架 - 通过在制造后将时钟到达时间偏移到锁存元件,将更快的阶段的时间松弛转移到较慢阶段。

因此,管道可以以接近平均阶段延迟的时间进行计时,而不是最长的时间。

此外,ReCycle的频率增益随着捐助者阶段的增加而增强,

这些都是空白的阶段,将“慷慨捐赠”放在缓慢的阶段。

最后,ReCycle还可以将松弛转换为功率降低。

对于17FO4管道,ReCycle将频率提高了12%,平均应用性能提高了9%。

结合ReCycle和捐赠阶段,平均提高了36%的频率和15%的性能,完全回收了由于变化造成的性能损失。

1.介绍

过程变化是在45纳米范围内继续缩放集成电路技术的主要障碍。

随着晶体管尺寸的不断缩小,精确地控制制造工艺变得越来越困难。

因此,同一芯片中的不同晶体管表现出不同的参数值,例如阈值电压或有效通道长度。

这些参数又决定了晶体管的开关速度和泄漏,晶体管也受到很大的波动。

晶体管切换速度的变化在架构层面上是可见的,当它使处理器中的某些单元太慢以至于无法满足时序时,迫使整个处理器以比标称频率低的频率工作。

变化已经迫使设计师采用保护条带,随着技术的发展,利润越来越大。

鲍曼等人 建议变更可能会消除全面技术一代的业绩增长。

仔细的时序设计在最先进的处理器管道中尤其重要。

许多考虑因素都会影响到什么阶段的选择和什么时钟周期的影响[21,23,42]

随着过程变化,一些阶段的逻辑路径变慢,制造后其他阶段的逻辑路径变得更快,加剧了管道不平衡,降低了管道可达到的频率。

流程变化的一般问题的当前解决方案可以大致分为电路级和架构级技术。

在电路层面,有多种提出的技术,包括自适应主体偏置(ABB)和自适应电源电压(ASV)缩放。

这些技术在许多情况下是有效的,尽管它们增加了制造过程的复杂性并且具有其它副作用。

具体来说,ABB提高频率会增加泄漏功率,并通过ASV来实现对终端可靠性的破坏性影响。

架构级技术是电路级技术的补充。 然而,迄今提出的大多数目标是针对少量功能块,即寄存器文件和执行单元以及数据高速缓存。 其他技术集中在重新设计锁定元件[17,46]。 这些技术可能涉及大量设计工作和硬件开销。

在本文中,我们建议以架构级技术来容忍流程变化对处理器管线的影响:(i)不会对泄漏或硬件可靠性产生不利影响,(ii)全局适用于流水线中的所有子系统,以及 (iii)硬件开销微乎其微。 它是基于循环时间偷窃的综合应用[4],其中通过将时钟到达时间偏移到锁存元件,流水线中较快阶段的时间松弛被转移到较慢的阶段。 因此,管道可以以接近平均阶段延迟的时间进行计时,而不是最长的时间。 我们称之为ReCycle方法,因为之前浪费在更快阶段的时间松弛现在被“回收”到较慢的阶段。

我们显示,ReCycle增加了管道的频率,而不改变管道结构,管道深度或晶体管的固有开关速度。 这种增加在管道越深处越高。 此外,ReCycle可以与Donor流水线阶段相结合,这些阶段是添加到管道中的关键环路的“空白阶段”,以便向慢速阶段“捐赠”松弛,从而增加管道频率。 我们也可以使用ReCycle将非关键管道环路的松弛推送到它们的反馈路径,然后在那里消耗,以减少线路功率或提高线路布线能力。 最后,ReCycle也可以用来挽救由于变化引起的保持时间故障否则会被拒绝的芯片。

我们的评估与没有和使用ReCycle的变化影响的管道进行比较。 平均来说,17FO4管道,ReCycle增加了12%的频率,从而恢复了变化频率损失的63%,并将应用程序加快了9%。结合ReCycle和捐赠阶段更加有效。 与没有ReCycle的管道相比,它的平均频率提高了36%,性能提高了15%,甚至比没有过程变化的管道更好。 最后,ReCycle还在反馈路径中节省了7-15%的功率。

本文的组织结构如下。 第2节给出了背景; 第3节,第4节和第5节分别介绍了ReCycle的想法,用法和实现。 第6节和第7节评估ReCycle;第8节讨论相关工作。

背景

管道时钟

管道设计中最具挑战性的任务之一是确保管道正确计时。 数据传播延迟和时钟周期必须使得在每个锁存元件中保持建立(T setup)和保持(T hold)时间。

通常,希望在循环时间允许的情况下,在流水线阶段中设置更多的逻辑。 这可以通过使用称为循环时间偷取技术[4]来改变流水线频率来实现。 使用这种技术,舞台利用分配给其后继或前身阶段的一部分时间。 典型地通过调整时钟到达时间来获得来自另一个阶段的强制移除时间。

考虑在触发器FF i(初始)之前的跟踪触发器FF f(最终)的流水线阶段。 舞台可以通过将FF f的时钟延迟一定时间或偏差delta;f,从后继阶段中窃取时间。 类似地,它可以通过将FF i的计时改变为负的偏差delta;i来从其前身阶段窃取时间。 在所有情况下,由于我们不改变周期时间,所以一个或多个阶段必须至少与被盗的数量一样多。

在循环时间偷窃下,建立和保持约束仍然得到满足。 假设该阶段的数据传播延迟为T延迟,管道的时钟周期为T CP。 FF i在时钟边缘产生的数据必须到达FF f,不迟于下一个时钟边沿到达FF f(等式1)之前的设置时间。 此外,FF i在时钟边缘产生的数据必须在FF f(等式2)到达FF之后的保持时间之前到达FF f。

delta; i T delay T setup le; T CP delta; f (1)

delta; i T delay ge; delta; f T hold

2.2 管道循环

管道环路是在管道的相同或较早阶段需要一个阶段的结果时出现的通信环路[5,10]。 环路是由数据,控制或结构危害引起的。 循环通常由一个或多个流水线阶段和将终端连接到初始阶段的反馈路径组成。

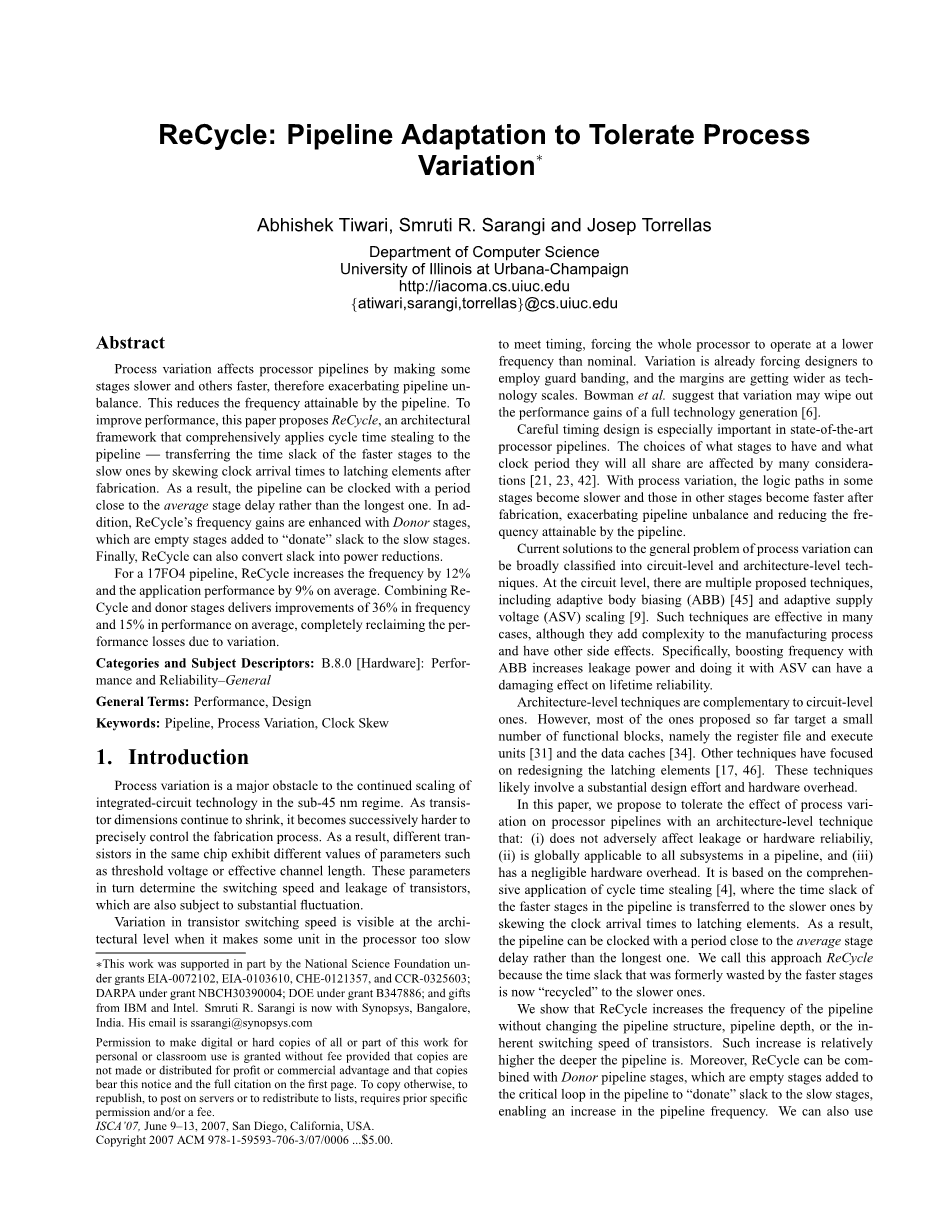

例如,图1(a)显示了我们用来演示ReCycle的Alpha 21264管道的简化版本[28]。 该图不显示管道的物理结构。 相反,它显示了一个逻辑结构。 每个长框代表一个逻辑阶段,而短框则是它们之间的流水线寄存器。 一些逻辑阶段被分解成多个物理阶段,如虚线所示。 逻辑级之间的线代表通信链路。

图1:Alpha 21264管道的简化版本,用于演示ReCycle:逻辑管道结构(a)和管道循环(b)。

该图描绘了前端阶段,然后从上到下,整数数据路径,加载存储单元和高速缓存以及浮点数据路径中的阶段。 虽然真正的处理器具有更多的通信链接,但我们只显示我们认为最重要或最重要的时间。 例如,我们不显示回写链接,因为回写时间更短。 反馈路径被标记。

图1(b)描述了简化流水线中的管道回路。 前两列的名称和描述分别是循环。 接下来的两列显示了创建循环和循环组件的反馈路径。

请注意,我们的循环与[5,10]中的循环不完全相同。我们检查一个更复杂的流水线,并没有显示所有的通信链接。 特别地,我们只显示我们认为最重要的反馈路径。 例如,我们不显示所有转发路径。 虽然我们将分析这个简化的流程,但ReCycle通用到适用于更复杂的管道。

虽然过程变化存在于几个层次,但我们专注于由于光刻不规则和由于掺杂剂浓度变化引起的随机效应的系统效应引起的内模(WID)变化[43]。 系统变化表现出强烈的空间相关性 - 靠近在一起的结构可能具有相似的值 - 而随机变化则不具有。

受变化影响的两个重要工艺参数是阈值电压(Vt)和有效通道长度(L eff)。 这些参数的变化直接影响门功率模型给出的门延迟(T g)[38]:

其中mu;是载流子迁移率,Vdd是电源电压,alpha;通常为1.3。 mu;和Vt都是温度T的函数。

我们分别处理随机和系统变化。 我们用具有特定相关结构的多变量正态分布来模拟V t的系统变化[43]。 它的特征在于三个参数:mu;,sigma;sys和phi;。 具体来说,我们将芯片分为1M个单元格。 每个单元采用由参数mu;和sigma;sys的多变量正态分布给出的V t的单个值。 与此同时,V t在空间上相关。

我们假设相关性是各向同性的,与位置无关[47]。 这意味着网格中两点〜x和y之间的相关性取决于它们之间的距离,而不是方向或位置。 因此,我们将V t(〜x)和V t(〜y)的相关函数表示为rho;(r),其中r = |〜x - 〜y |。定义,rho;(0)= 1 完全相关)。 我们还设置rho;(infin;)= 0(即完全不相关)。 然后我们假设rho;(r)随着球面分布[r]的变化。 在球面分布中,rho;(r)平滑地从1减小到0,在所谓的距离范围内达到0。 直观地,这意味着在距离phi;处,两个晶体管的V t之间没有显着的相关性。 这种方法匹配了Friedberg等人获得的经验数据[19]。 Phi;作为芯片宽度的一部分给出。

Vt的随机变化发生在比系统变化更精细的颗粒度:它发生在单个晶体管的水平。我们将其建模为具有sigma;rand和零平均值的不相关的正态分布.L eff被建模为具有不同mu;的V t ,sigma;sys和sigma;rand,但phi;相同。。

从Vt和Leff变化,我们使用公式3计算T g变化。然后我们使用Bowman等人的关键路径模型。 [6]估计每个流水线阶段支持的频率。 该模型采用关键路径中的门数(n cp)和结构中的关键路径数(N cp),并计算结构中最长关键路径延迟(max {T cp})的概率分布。 这是确定结构的最大频率的路径,我们设置为1 / max {T cp}。

为简单起见,我们将关键路径建模为通过非常短的电线连接的n cp FO4门 - 其中n cp是流水线阶段的有用逻辑深度。 不幸的是,准确估计每个流水线阶段的N cp是困难的,因为N cp是设计特定的,并且不能公开提供给设计。 因此,我们假设关键路径在处理器布局上以空间均匀的方式分布 - 除了在L2中,其路径决不会影响周期时间。 从每个流水线阶段的布局区域和Bowman等人估计,我们技术节点的高性能处理器芯片具有约10,000个关键路径[6],我们确定了每个阶段的关键路径。 阶段中最慢的关键路径决定舞台的频率; 最慢的阶段决定了管道的频率。

3.使用ReCycle进行管道适配

3.1主要思想

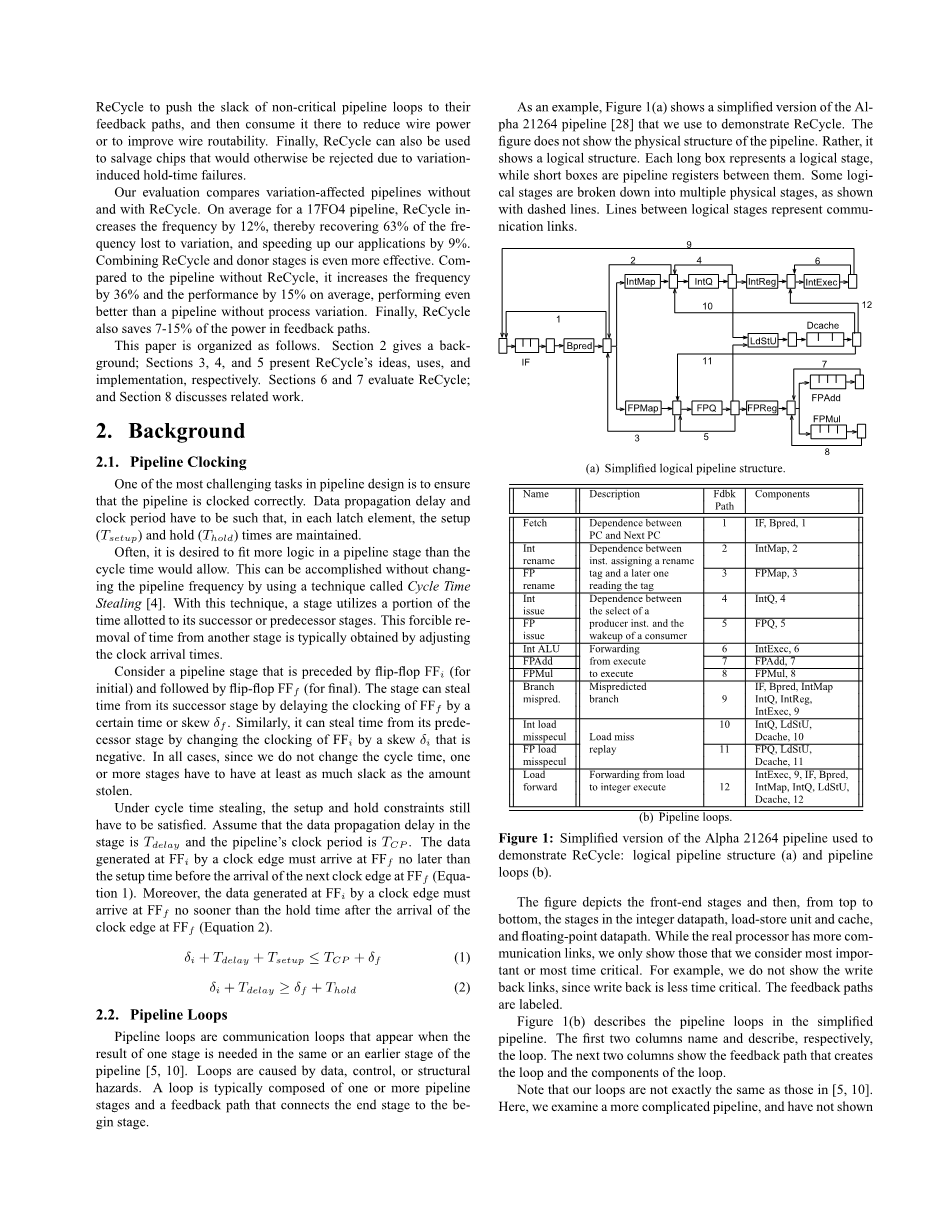

要了解ReCycle背后的想法,请考虑图2(a)的流程,并调用T i在第i阶段执行工作所需的时间。 为了简单起见,在没有过程变化的情况下,我们假设T i对于所有i都是相同的,因此,管道的周期是T CP = T i,forall;i。 当变化设置时,它会减慢一些阶段,同时加速其他阶段。 如图2(a)所示,所得到的不平衡流水线必须以更长的时间T CP = Max(T i),forall;i计时。

图2:流程变化对管道(a)和偏斜的影响

时钟信号(b)。

通过ReCycle,我们全面应用循环时间窃取来纠正这种变化导致的管道不平衡。 流水线的结果时钟周期为T CP = Average(T i),forall;i。 这个时期可能与无变化流水线的时间类似。如图2(a)所示,慢阶段的传播速度要比传统信号的时钟周期多一个时钟周期,而是以更快的速度转移它们的松弛。

通过这种方法,我们不需要改变管道结构,流水线深度或晶体管固有的开关速度。图2(b)描绘了一个慢阶段的时序图,显示了其初始流水线寄存器的时钟信号, 其最终注册(后者没有和与ReCycle)。 舞台中的数据传播可以采取一定范围的延迟(D min,D max),具体取决于它使用的路径。 该范围显示为阴影锥。 没有ReCycle,该图显示信号可能需要太长时间才能被最终寄存器锁存。

使用ReCycle,最终寄存器的时钟被延迟了T个偏移.T偏移被选择,使得即使信号采用D max,它到达最终寄存器足够早以满足建立时间(T setup)(图2b))。 由于时钟周期小于D max,所以两个信号可以以波浪流式方式同时存在于一级逻辑中[11]。 这可以通过两个信号的锥体在时间上重叠的事实来看出。 另外,最小延迟D min必须足够长,以便满足最终寄存器的保持时间(T hold)(图2(b))。

一般来说,我们会偏移舞台的初始和最终的寄存器的时钟。 根据2.1节,我们分别称这种偏差delta;i和delta;f。 因此,图2(b)中的T偏移是delta;f-delta;i。在慢阶段,delta;fgt;delta;i; 在一个快速的,delta;f lt;delta;i。 为了使ReCycle工作,流水线中的所有阶段必须满足方程1和2的设置和保持约束,其以D min和D max表示,可以重写为:

在一个实际的管道中,这个简单的模型由于管道不是单个线性链阶段而变得复杂化。 相反,如图1(a)所示,流水线用于生成子流水线(例如,整数和浮点流水线),并通过反馈路径(例如,分支错误预测循环)循环回到前一级。

使用ReCycle,如果参与循环,阶段只能交易松弛。 例如,在图1(a)中,IntExec和Bpred阶段可以交换松弛,因为它们属于分支错误预测循环。 然而,IntExec和FPAdd阶段不能交易松弛.

3.2. 寻找最佳时期

给定一个任意的流水线,我们想找到我们可以将其定时的最短时钟周期T CP以及我们需要应用到不同流水线寄存器的时间偏差delta;的集合,以使其成为可能。 方程4和5的设置和保持约束是线性不等式。 因此,找到最佳周期和偏差的问题可以被制定为线性程序,其中我们最小化T CP,受制于管线中所有阶段的建立和保持约束。

在该线性程序中,未知数是T CP和每个单独阶段的初始和最终流水线寄存器的偏差(delta;i和delta;f

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[139840],资料为PDF文档或Word文档,PDF文档可免费转换为Word

您可能感兴趣的文章

- 饮用水微生物群:一个全面的时空研究,以监测巴黎供水系统的水质外文翻译资料

- 步进电机控制和摩擦模型对复杂机械系统精确定位的影响外文翻译资料

- 具有温湿度控制的开式阴极PEM燃料电池性能的提升外文翻译资料

- 警报定时系统对驾驶员行为的影响:调查驾驶员信任的差异以及根据警报定时对警报的响应外文翻译资料

- 门禁系统的零知识认证解决方案外文翻译资料

- 车辆废气及室外环境中悬浮微粒中有机磷的含量—-个案研究外文翻译资料

- ZigBee协议对城市风力涡轮机的无线监控: 支持应用软件和传感器模块外文翻译资料

- ZigBee系统在医疗保健中提供位置信息和传感器数据传输的方案外文翻译资料

- 基于PLC的模糊控制器在污水处理系统中的应用外文翻译资料

- 光伏并联最大功率点跟踪系统独立应用程序外文翻译资料