英语原文共 9 页,剩余内容已隐藏,支付完成后下载完整资料

740 IEEE TRANSACTIONS ON COMPONENTS, PACKAGING AND MANUFACTURING TECHNOLOGY, VOL. 6, NO. 5, MAY 2016

非均匀集成 InGaP/GaAs HBTs的热设计和特性

Sukwon Choi, Gregory M. Peake, Gordon A. Keeler, Member, IEEE, Kent M. Geib, Ronald D. Briggs,

Thomas E. Beechem, Ryan A. Shaffer, Jascinda Clevenger, Gary A. Patrizi, John F. Klem, Senior Member, IEEE,

Anna Tauke-Pedretti, and Christopher D. Nordquist, Senior Member, IEEE

摘要—本文研究了在宽禁带AIN衬底上集成热管理的n-p-n型InGap/GaAs异质结双极晶体管(HBTs),并对其去除GaAs衬底进行了研究。在没有热管理的情况下,集成后的衬底去除严重加剧了自热效应,由于器件自热过度,导致I–V特性差。本文提出了一种涉及仿真(设计)、热特性表征、制造和评价的电热协同设计方案。利用热反射热成像、基于电-温度敏感参数的温度测量和红外热成像来评估HBTs在不同配置下的结温升。为了降低集成器件的热阻,采用结构改造辅助的被动冷却方案,即在器件与载体之间定位锢凸块散热器这个方法得到使用。通过在靠近倒装芯片集成HBTs的活动区域实施热散热器,连接点到基板的热电阻降低了两倍,这是由连接点温度测量和电气性能的改善所揭示的。本文所提出的非均匀集成方法不仅考虑了电的需求,还考虑了热的需求,为实现先进的、鲁棒的、非均匀集成电子器件提供了思路。

关键词—III–V半导体材料,异质结双极晶体管(HBTs), 红外 (IR)成像, 集成电路技术,温度测量, 电子热反应成像的热管理。

稿件由2015年7月27日收到,在2015年12月29日修改,于2016年2月11日被采纳。2016年4月20日出版:现刊日期2016年5月13日。Sandia国家实验室是一个多项目实验室,由洛克希德·马丁公司的全资子公司Sandia公司管理和运营,隶属于美国能源部国家核安全管理局,合同编号为DE-ACO4-94AL85000。由副主编C.C.Lee根据审稿人的意见推荐出版。

S.Choi就职于Sandia美国阿尔伯克基国家实验室,编号87185。他现在就职于宾夕法尼亚州立大学。(电子邮件:sukwon.choi@psu.edu)

G. M. Peake, G. A. Keeler, K. M. Geib, R. D. Briggs, T. E. Beechem,

R. A. Shaffer, J. Clevenger, G. A. Patrizi, J. F. Klem, A.Tauke-Pedretti,and C. D. Nordquist 就职于美国阿尔伯克基市桑迪亚国家实验室, (电子邮箱: gmpeake@sandia.gov; gakeele@sandia.gov;kmgeib@sandia.gov; rdbrigg@sandia.gov; tebeech@sandia.gov; rshaffe@sandia.gov; jcleven@sandia.gov; gapatri@sandia.gov; jklem@sandia.gov;ataukep@sandia.gov; cdnordq@sandia.gov).

数字对象标识符 10.1109/TCPMT.2016.2541615

I.引言

采用不同的技术对各种各样的基于III-V有机半导体的异质结双极性晶体管(HBTs)融合,如光电子器件、微机电系统和CMOS电子器件等,都有可能得到功能性改进和增强的能力,特别是Ⅲ-Ⅴ电子学与传统高密度硅的CMOS电路在高频性能和功率增益方面无法比拟的异质集成,可以提高混合信号和射频电路[1]的性能。

III–V材料与硅的集成已经引起了人们几十年的兴趣,并取得了不同程度的成功。但是,目前还没有大规模的技术。为了达到这一目的,器件转移或外延转移方法是很有前途的。器件转移是一种成熟的技术,通常用于光学和光子器件与其它电路的集成。最相关的例子是使用倒装芯片将单个芯片组装到CMOS晶圆[2]上。使用预生长外延的衬底转移较少,但它提供了更紧密的集成,最小化器件寄生电容和衬底损耗[3]。

尽管存在增强功能和功能的机会,但退化的热特性通常是3-D异构集成[4]的结果。为了保持单个器件的预集成电性能,必须在不同集成模块的早期设计阶段考虑器件的热阻。例如,基于GaAs和InP的HBTs提供了比硅CMOS或双极器件更高的驱动电压和更高的高速性能。然而,这些器件容易受到自热效应的影响,如单个器件的直流电流增益()随着的增加而降低,多指器件[5]的电流崩溃。GaAs衬底是相对较差的热导体,HBT结构的内部III–V三元复合材料的热导率比GaAs[6]低一个数量级。这些因素导致热问题的加剧,不仅会降低器件的性能,还会影响器件的可靠性。因此,热管理是实现高性能GaAs或InP HBT异构集成的关键因素。

在本文中,我们探讨了热管理的挑战和基于砷化镓的HBT技术的潜在解决方案,该技术是通过将倒装芯片粘接到一个绝缘的、高导热的、主要的倒装芯片载体上进行非均匀集成。这个设备转移过程包括一个额外的步骤砷化镓衬底去除,以改善大小,重量和功率。为了降低芯片的热阻,采用了被动冷却方案。

2156-3950 copy; 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

See http://www.ieee.org/publications_standards/publications/rights/index.html for more information.

CHOI et al.: THERMAL DESIGN AND CHARACTERIZATION OF HETEROGENEOUSLY INTEGRATED InGaP/GaAs HBTs 741

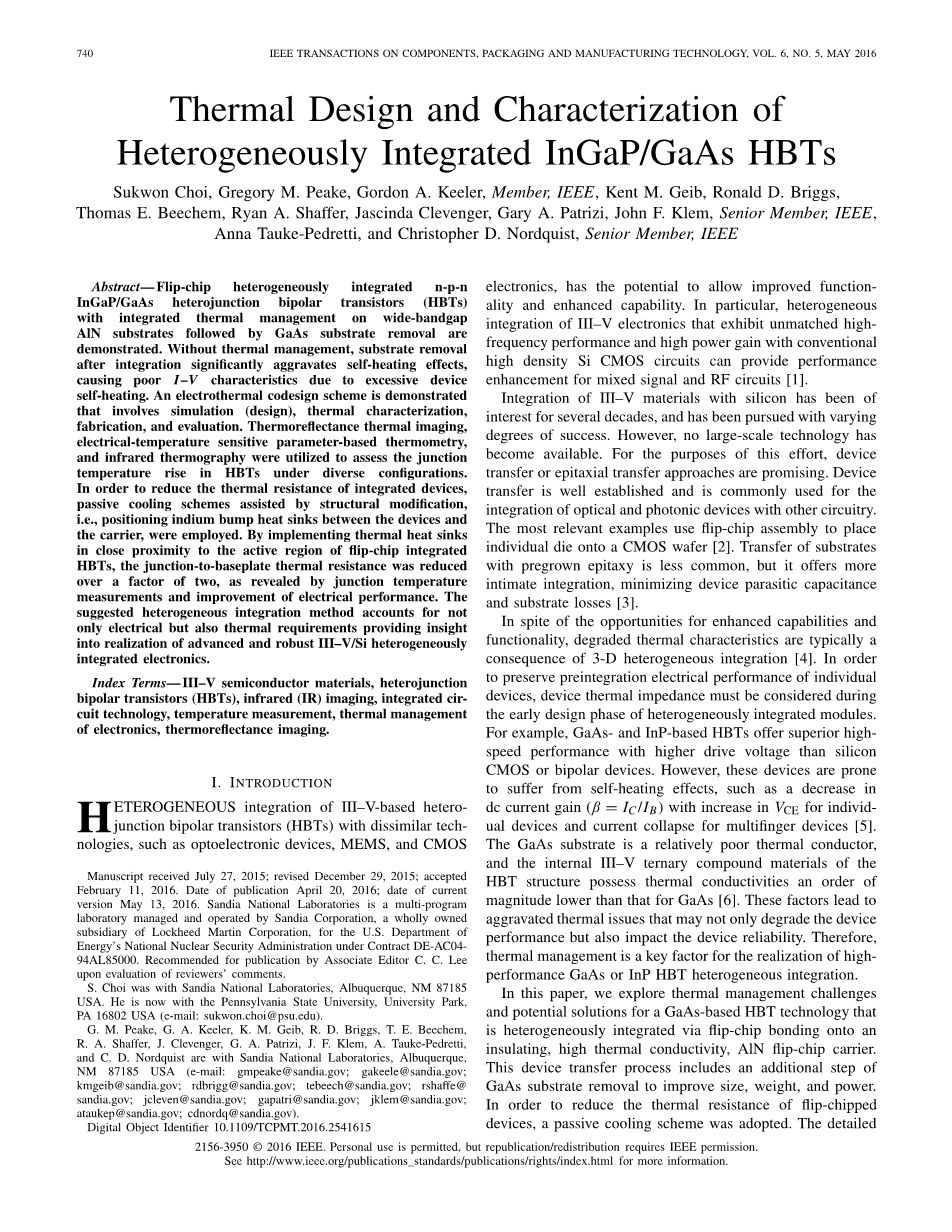

图1.将GaAs HBT模具连接到载体上并移除基板的集成方法的截面示意图。 (a)上层甲板处理的HBT在设备下方有一层蚀刻停止层,绝缘层有开口(两者均未显示)和粘合金属(不按比例)。(b)用配合凸点将芯片翻转到主载体上(未显示发射极键合垫下的铟凸点),填充设备与载体之间的空隙,移除基板(未按比例)。(c)将HBTs转移到AIN载体上并去除基板的光学显微摄影。

为了设计目的,本文进行了详细的热模拟。为了验证模型并评估热解的有效性,将仿真结果与温度进行了比较。测量方法包括热反射热成像、电-温敏感参数(E-TSP)测温和红外热成像。

Ⅱ.混合集成HBT器件

通过分子束外延生长了InGaP/GaAs n-p-n型HBT器件的外延层,所需的GaAs子集电极、GaAs集电极、GaAs基极和InGaP发射极层依次沉积在未掺杂的半绝缘GaAs衬底上。选择发射极InGaP组合物以实现与砷化镓衬底的晶格匹配。基础是碳掺杂的p砷化镓。高掺杂/分级InGaAs接触层生长在发射极上,形成低电阻欧姆接触。此外,为了减少表面复合,还建立了InGaP发射极层作为外部基底区域的钝化层。发射面积为。通过适当的刻蚀层和金属触点的沉积来完成结构。采用自旋对苯并环丁烯(BCB)实现能级间二极化。标准排放的更多细节。在[5]和[7]中可以找到HBTs的构型及其制造工艺。

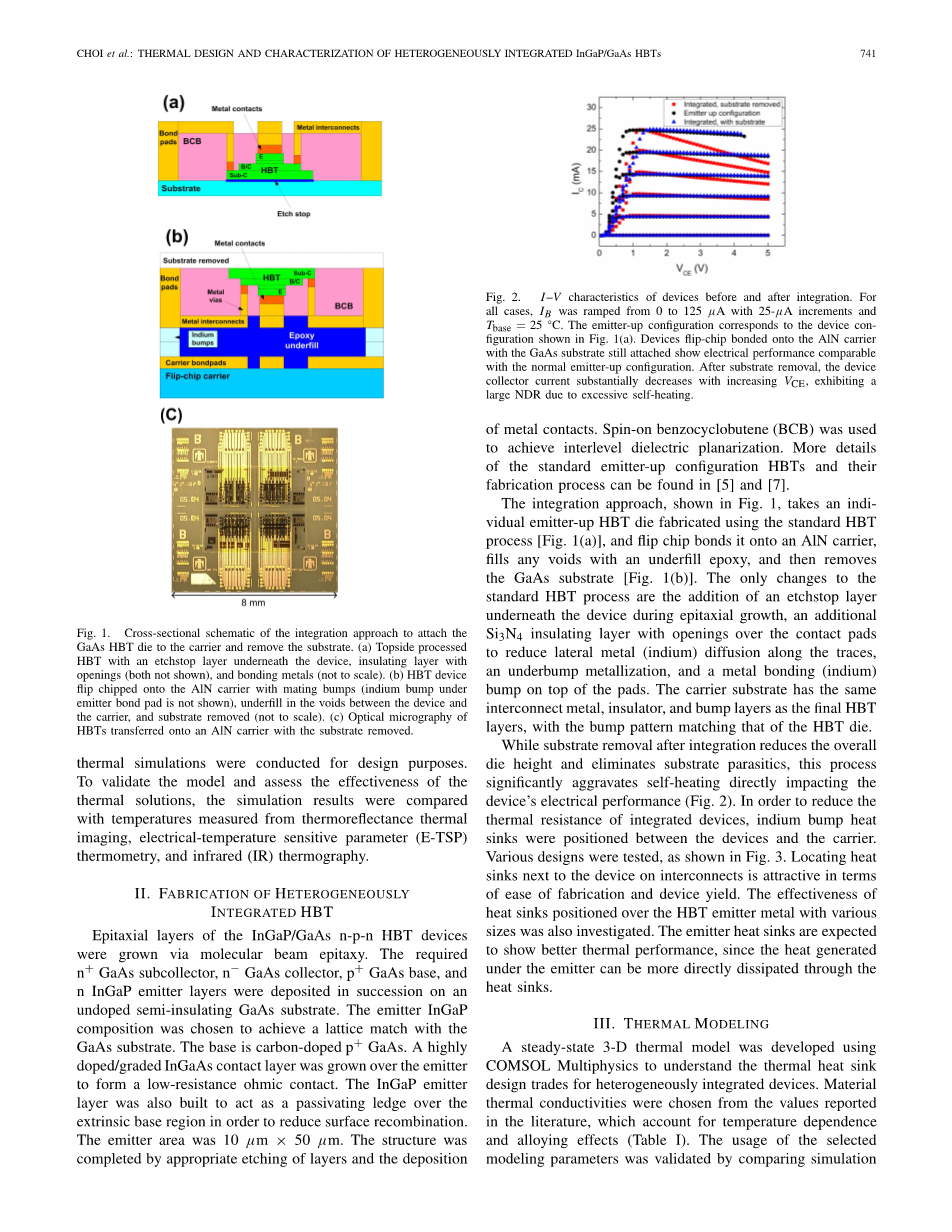

图2.设备集成前后的I-V特性。所有例子中,从O增加25mu; A至125mu; A,=25℃。排放装置的启动配置与图1(a)所示的设备配置。与砷化镓衬底仍然附着在主载体上的倒装芯片显示的电气性能可与正常的发射装置相媲美。除去衬底后,器件集电极电流大大减小。增加,由于过度的自热而表现出较大的NDR。

集成方法如图1所示,采用标准HBT工艺制作的单个排放型HBT模具[图1(a)],倒装芯片将其粘接在AIN载体上,用填充不足的环氧树脂填充任何空隙,然后去除GaAs衬底[图1(b)]。标准HBT工艺的唯一变化是在外延生长过程中在设备下方增加了一个蚀刻停止层,在接触垫上增加了一个开孔的SigN4绝缘层,以减少金属(铟)沿轨迹的横向扩散,一个下凸包金属化,以及一个金属焊接(铟)在焊盘上发生碰撞。载体衬底具有与最终HBT层相同的互连金属绝缘体和凹凸层,凹凸图案与HBT模具相匹配。

集成后去除衬底降低了整体模高,消除了衬底寄生,但这一过程明显加剧了直接影响器件电气性能的自热(图2)。为了降低集成器件的热阻,在器件与载体之间设置了铟凸块散热器。对各种设计进行测试,如图3所示。在互连时将散热器放置在器件旁边,在制造方便和器件成品率方面很有吸引力。还研究了在不同尺寸的HBT发射金属上放置散热器的有效性。由于在发射体下产生的热量可以通过热沉更直接地消散,因此预计发射极散热器将表现出更好的热性能。

Ⅲ.热建模

利用COMSOL Multiphysics建立稳态三维热模型,研究了非均匀集成器件的热沉设计问题。材料热导率值选择了在文献中报道,占的温度依赖性和合金化的影响(表1)。使用所选的建模参数的仿真结果进行了比较,验证了温度测量的实验技术在第四节详细。热代(从0.05到0.25W)被认为发生均匀在足迹的立方体积等于发射极区域,垂直地从基极-发射极结向下延伸到集电极/子集电极接口。为了简化模型,忽略了有限基极电阻引起的发射极带边缘的发射极电流拥挤现象,从而假定热源在发射极宽度上是均匀的。对于标准的发射装置,假设基板下的基底温度为50℃,以匹配用于热表征的实验参数。

742 IEEE TRANSACTIONS ON COMPONENTS, PACKAGING AND MANUFACTURING TECHNOLOGY, VOL. 6, NO. 5, MAY 2016

IV. 实验测温技术

图3. (a) 倒装芯片集成器件的散热片设计,其基板被移除。

(b)选定的三维表示。

表1.导热系数

对于倒装芯片集成器件,采用相同的载体基面等温温度边界条件。所有其他暴露在室温(22℃)下的表面,采用自然对流边界条件()。模型的几何形状是基于实际的器件掩模布局,尽量简化假设,因为金属痕迹和通孔结构在传热中起着至关重要的作用,尤其是在倒装芯片集成器件中。包括图1在内的横截面图中没有表示通孔和接口层的详细信息。

通过热反射热成像、E-TSP测温和红外热成像进行了器件温度测量。进行这些测试是为了确认用于为集成器件模块设计热解决方案的热模型的有效性。还通过标准直流特性评估了热管理方面的改进。

- 热反射热成像

热反射热成像检测材料表面反射率随温度升高的变化。由于大多数材料的热反射系数[15]非常小,因此采用锁定技术来增强信噪比,以获得良好的温度图像。

利用Microsanj NT210B测量了不同结构下hbt的温升。在锁定信号频率为1khz的情况下,使用周期性的10%占空比方电压脉冲()操

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[607048],资料为PDF文档或Word文档,PDF文档可免费转换为Word

您可能感兴趣的文章

- 饮用水微生物群:一个全面的时空研究,以监测巴黎供水系统的水质外文翻译资料

- 步进电机控制和摩擦模型对复杂机械系统精确定位的影响外文翻译资料

- 具有温湿度控制的开式阴极PEM燃料电池性能的提升外文翻译资料

- 警报定时系统对驾驶员行为的影响:调查驾驶员信任的差异以及根据警报定时对警报的响应外文翻译资料

- 门禁系统的零知识认证解决方案外文翻译资料

- 车辆废气及室外环境中悬浮微粒中有机磷的含量—-个案研究外文翻译资料

- ZigBee协议对城市风力涡轮机的无线监控: 支持应用软件和传感器模块外文翻译资料

- ZigBee系统在医疗保健中提供位置信息和传感器数据传输的方案外文翻译资料

- 基于PLC的模糊控制器在污水处理系统中的应用外文翻译资料

- 光伏并联最大功率点跟踪系统独立应用程序外文翻译资料