英语原文共 7 页,剩余内容已隐藏,支付完成后下载完整资料

高分辨率和快速通过时间的x射线计算机断层扫描在半导体封装上的应用

摘要

综述了三维X射线计算机断层扫描在微电子封装中的最新应用, 包括无损failure analysis, defect monitoring in solder 失效分析、焊点和铜通孔的缺陷监测and Cu vias, and progressive reliability study of solder ,以及焊料空隙的渐进可靠性研究,electron migration induced void nucleation in solder join电子迁移引起的焊点空洞形核和铜通孔空洞的形成。高分辨率和无损的三维X射线CT数据在封装工艺开发、质量控制和可靠性风险评估方面具有很高的价值;然而,目前实验室规模的三维X射线CT技术由于其亮度低、非平行X射线束导致数据采集时间长,局限于微米级分辨率的约1-2mm2局部区域。另一方面,X射线同步源可以提供大面积高亮度的准直光束,该准直光束允许在3-20分钟内成像包括硅、填充不足、多层焊点、介电层、铜通孔以及多个基板中的通孔的整个3D封装。本文讨论了当前三维X射线CT技术的局限性,以及三维封装同步X射线研究所提供的下一代三维X射线CT技术的发展方向。

介绍

半导体行业对更高集成水平、更低成本的要求以及对完整系统配置的日益增长的需求,导致了对具有更高电路密度、更小尺寸和更低Z高度的3D电子封装解决方案的持续驱动。由于半导体封装中的复杂性增加,互连尺寸减小,无损和高分辨率分析技术对半导体封装失效分析、封装技术开发、质量控制和可靠性风险评估是非常理想的。

实验室规模的三维X射线计算机断层扫描(CT)技术已被成功证明能够在完整样品中检测分辨率为微米范围的封装组件中的缺陷。尽管在分辨率方面取得了良好的进展,但通入时间(TPT)仍然很长,每1-2平方毫米感兴趣的区域需要数小时的数据采集时间。这严重限制了3D X射线CT在半导体封装中的应用,因为封装尺寸通常在100-3600平方毫米之间。

综述了目前实验室规模的三维X射线CT在微电子封装中的应用,包括无损失效分析、焊点或铜通孔缺陷监测以及渐进可靠性研究。讨论了目前X射线CT技术的局限性。

本文介绍了近年来利用同步辐射X射线CT进行三维封装的研究,为今后的改进提供了方向。高亮度同步辐射X射线源具有大面积准直光束,在比传统光源大得多的区域提供高分辨率X射线成像。结果表明,整个16x16毫米封装系统(SIP)可以在3到20分钟内成像。

实验室级X射线CT工作原理

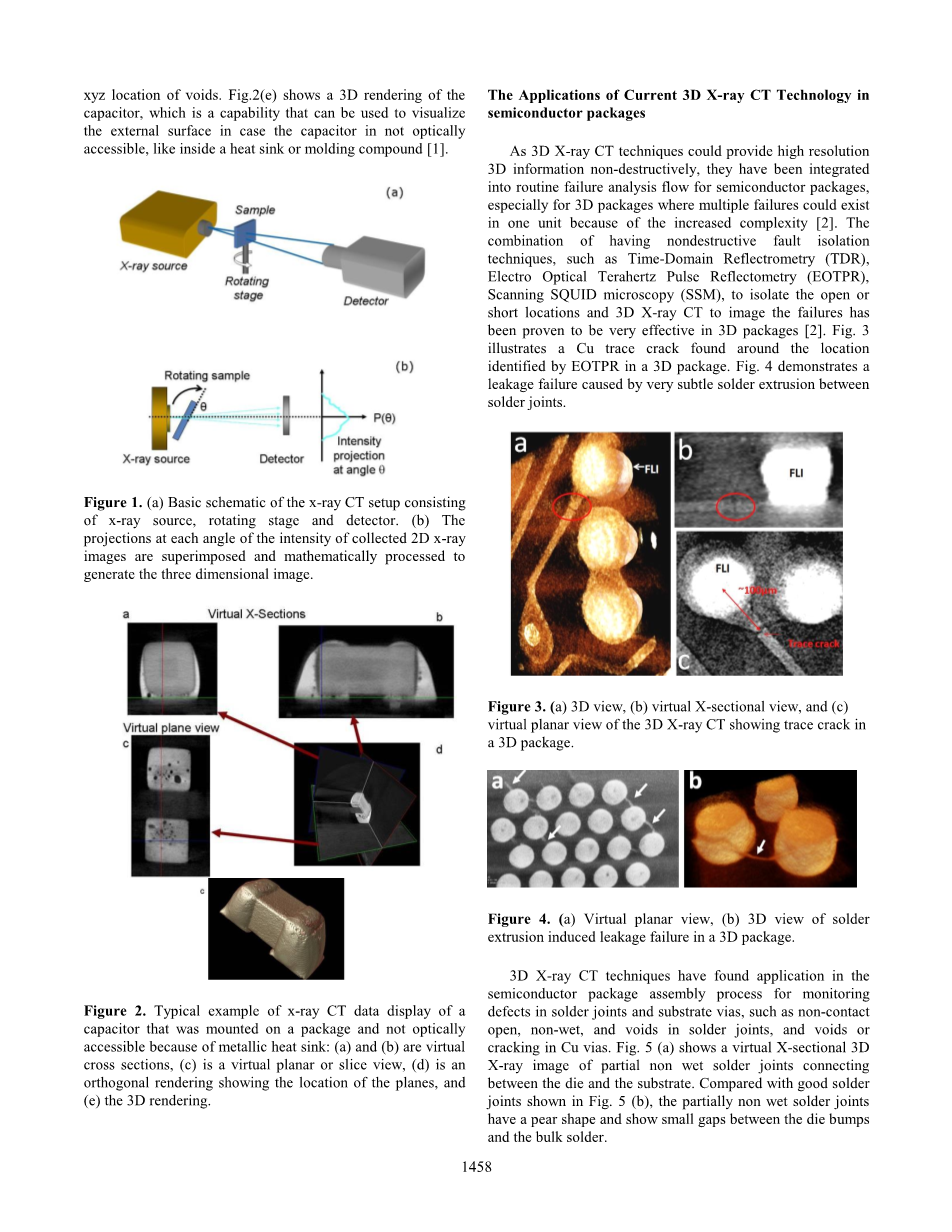

已经提出并开发了各种用于半导体应用的工业X射线CT系统,其缺陷检测能力从一微米到几微米不等,具体取决于所用的具体配置。X射线CT系统的基本设置如图1(a)所示,由一个辐射物体的X射线源形成,该X射线源安装在提供离散角位移的旋转台上,以及一个检测子系统,该子系统捕获每个角度的二维X射线图像。然后对所有图像进行数学处理,以在3D中重建对象[1]。

由于处理后的数据包含被测样品的体积信息,分析人员可以对其进行操作,以在三维数据集的任何给定位置显示虚拟截面或切片视图。这提供了消除视场中可能掩盖了单个二维X射线图像中缺陷产生的信号的干扰特征的能力;X射线CT作为一种分析方法的突出特点是,当把每个二维图像中包含的缺陷的细微信息添加到以等间距角度采集的整个图像集中特定XYZ位置的信号贡献中时,它变得非常重要。图2显示了电容器的典型虚拟横截面、切片或平面和正交视图的示例;注意图2(a)和图2(b)中的虚拟截面如何提供焊点空隙形状和XYZ定位的详细信息,而虚拟平面图2(c)显示了隐藏在高X射线吸收电容器下面的空隙。正交视图(图2(d))有助于分析者想像空隙xyz的位置。图2(e)所示为电容器的3D呈现,该功能可用于在电容器不可光学接近的情况下(如在散热片或成型化合物内部)显示外表面[1]。

图1.(a) X射线CT装置的基本原理图,包括X射线源、旋转台和探测器。(b)将采集的二维X射线图像各角度的投影进行叠加和数学处理,生成三维图像。

图2.安装在封装上的电容器的X射线CT数据显示的典型示例,由于金属散热片而无法进行光学访问:(a)和(b)是虚拟截面,(c)是虚拟平面或切片视图,(d)是显示平面位置的正交渲染,以及(e)3D渲染。

当前三维X射线CT技术在半导体封装中的应用

由于三维X射线CT技术能够无损地提供高分辨率的三维信息,因此它们已被集成到半导体封装的常规故障分析流程中,尤其是对于一个单元中由于复杂性增加而可能存在多个故障的三维封装[2]。将时域反射法(TDR)、太赫兹脉冲反射法(EOTPR)、扫描SQUID显微镜(SSM)等非破坏性故障隔离技术相结合,隔离开路或短路位置,并利用3D X射线CT对故障进行成像,已证明在3D封装中非常有效[2]。图3显示出了在三维封装中由EOTPR识别的位置周围发现的铜痕裂纹。图4显示了由焊点之间非常细微的焊料挤压造成的泄漏故障。

图3.(a)三维视图,(b)虚拟X截面视图,以及(c)显示三维封装中痕迹裂纹的三维X射线CT的虚拟平面视图。

图4.(a)虚拟平面图,(b)三维封装中焊料挤压导致泄漏故障的三维视图。

三维X射线CT技术已在半导体封装过程中得到应用,用于监测焊点和基板通孔中的缺陷,如非接触打开、非湿润和焊点中的空隙,以及铜通孔中的空隙或开裂。图5(a)显示了连接在晶元和基板之间连接的部分非湿焊点的虚拟X截面3DX射线图像。与图5(b)所示的良好焊点相比,部分非湿焊点呈梨形,并且在凹模凸起和大块焊点之间显示小间隙。

图5.(a),(b)具有部分非湿焊点和良好焊点的焊点的虚拟X截面图。

消除或减少焊料中的空隙量对于3D封装来说变得至关重要,因为焊点互连的直径要比传统半导体封装中的直径小得多,并且一级焊点在组装过程中通常需要经历更多的回流。传统的二维X射线技术不能在最佳情况下捕获直径小于5mu;m的空洞,也不能区分重叠的空洞,因此使用三维X射线CT监测焊点空洞对于开发三维封装的焊接工艺非常重要。图6显示了具有多个焊接空洞的焊接接头的三维视图,可以从三维X射线CT图像中获得空洞大小和位置,这为进一步的工艺改进提供了有价值的信息。

图6.具有多个焊接空隙的焊接接头的三维视图。

消费电子产品的小型化和便携性推动了下一代基板技术具有更高的电路密度、更小的尺寸和更低的Z高度。由于复杂度的增加,在工艺开发阶段,经常会出现诸如基板铜通孔和裂纹等缺陷。由于缺陷通常小于5mu;m,因此在基板组装过程中通常采用三维X射线CT对缺陷进行监测。图7表明,3D X射线CT能清晰地捕捉到小基板铜通孔中的空隙和裂纹。

图7.(a)基板铜通孔中空隙的虚拟X截面图。(b)铜通孔裂纹的三维视图。

三维X射线CT能够无损地提供半导体封装的高分辨率信息,使封装元件在可靠性应力(如回流、温度循环和高温下的一致电流)下的研究得以进行。利用三维X射线CT[3]研究了多次回流过程中的焊锡空洞生长动力学。如图8所示,在附加回流焊后组装过程中,相同的焊料空隙的增长非常明显。

图8(a)、(b)回流焊前焊点的虚拟X截面图和虚拟研磨图。(c),(d), 焊点再流焊后的虚拟X截面图和虚拟研磨图相同,分别显示了附加再流焊后组装期间焊点空隙的增长。

高温电流下焊点中的气孔形核和生长是半导体封装发展过程中的重点研究领域之一。渐进式三维X射线CT研究可提供时间零点和电气试验中间读数时的空隙位置和大小。正如在图9(a)-(d)所示, 由于电子迁移,在电气测试过程中,焊点中的空隙开始在阴极处形核和生长。从三维X射线CT图像中可以获得空洞生长动力学,可用于有效的可靠性风险评估。

图9(a), (b), (c), (d) 同一焊点在电流一致、时间零点温度升高的情况下的虚拟研磨图,以及中间读数。

长径比较大的铜通孔在电解充铜过程中会形成空洞。在电气测试之前和过程中,3D X射线CT被用于表征铜通孔中的空隙,在高温下对铜通孔施加一致的高电流,以捕捉空隙演化的性质[4]。如在时间零点拍摄的X射线CT虚拟横截面图像(图10(a))所示,在基板芯两侧的底层(bl)和顶层(tl)之间的铜通道中存在一个倒钥匙孔形状的空隙。图10(b)所示为150°C下3A电流1000小时后的铜通孔(如图10(a)所示)的相同虚拟截面图。图10(c)和10(d)分别显示了通过试验后相同铜的另一个虚拟X截面图和虚拟研磨图。三维X射线CT数据清楚地表明,在施加的大电流(即铜通孔的阳极)下,铜通孔末端基板的TL层中的空隙迁移和聚集为大空隙。基于三维X射线CT渐进数据研究了孔隙演化动力学[4]。

图10.(a)时间零点处的铜通孔的三维X射线CT虚拟X截面图像。(b) 在150°C下,在3A电流流动1000小时后,同一个铜通孔的相同虚拟X截面图。(c)电气试验后相同铜的另一个X截面图。(d)经过1000小时的电气测试后,同一个CU的虚拟平面图。

当前三维X射线CT技术的局限性

目前的三维X射线CT技术可以在半导体封装中无损地提供高分辨率的三维信息,已应用于电子封装的失效分析、过程控制和动力学研究领域;然而,与破坏性分析方法相比,这种技术确实有一些局限性,使其不那么理想。

首先,X射线源的光通量和亮度都很低,这会导致相对较长的曝光时间或图像捕获时间,从而延长高分辨率成像的TPT。为了获得具有合理的TPT的三维X射线图像,分析人员必须权衡视场(FOV)和图像质量以补偿长曝光时间。当一个样品中需要多个FOV或多个样品中需要一个FOV时,长TPT通常是显示止动器。在这些情况下,替代的破坏性分析方法提供了更快的信息获取时间。

另一方面,能量大于100kv的X射线束通常用于半导体封装成像,以处理高吸收的铜或焊料部件。这是因为束斑尺寸在更高能量下绽放,从而牺牲了分辨率。此外,高能X射线成像降低了相位对比度,也使有机封装材料隐形。这些因素限制了3D X射线CT在检测除Z值高的金属以外的封装材料中的缺陷时的使用,例如,硅开裂、填充不足的空隙或分层、成型化合物、阻焊剂和电子封装中的其他介电材料。

由于这些限制,开始对3D封装进行同步三维X射线CT研究,以同步辐射显微层析成像为起点,对整个3D系统级封装(SIP)进行成像,以探索具有所需X射线源的3DX射线CT的应用可能性[5]。

三维同步辐射CT操作

如图11所示,同步辐射CT的工作原理与实验室级CT基本相同,只是X射线源来自同步辐射源,而不是实验室级X射线管源。同步辐射束和实验室尺度束的原理区别在于,同步辐射具有极高的通量,具有单色的能力,具有大面积的足迹,可通过光学操作产生不同的分辨率,并且具有较长的焦距,因此X射线高度平行于低发散度[6]。这些因素组合成一个术语,称为光束亮度或亮度(光子通量除以散度、光束大小和能带宽度),可能比实验室尺度的光源高10个数量级[6]。CT同步加速器的主要优点是:由于高通量的存在,可以显著降低TPT;由于光束的大尺寸,可以检查更大的感兴趣区域;由于光束的低发散度,可以在很大的部分尺寸上保持图像质量;使用相对较低的能量水平的可能性使相衬成像成为可能。在这里,同步辐射束被用来成像一个完整的多层SIP包,同步辐射微断层成像作为参考点,并与传统的3DCT方法进行比较。

同步加速器工作在劳伦斯伯克利国家实验室先进光源(ALS)光束线8.3.2上进行。该光束线专门用于微断层扫描,X射线由超导弯曲磁铁产生,从能量为1.9gev,电流为500ma的储存环产生高通量X射线束。有关此光束的详细信息,请参阅文献[7]。在这些实验中,多色光束被用来使安装在成像光学前面旋转台上的样品的X射线通量最大化。穿过样品的X光照射在Luag单晶闪烁体上,闪烁体发出可见光。可见光图像是使用不同的放大镜(1、2、5和10x)由两个不同的相机中的一个(称为相机A(2560 x 2160像素的PCO边缘CCD成像相机)和相机B(4008 x 2672像素的PCO 4000 CCD成像相机)观看的。相机和镜头的不同组合产生不同的分辨率和视场(FOV),如表1所示。请注意,FOV随分辨率的增加而减小,此设置的最高分辨率为~0.65mu;m。

通过将样品以0.175°的角度增量旋转180°进行SIP包的3D CT同步成像,并在每个角度步骤记录图像。同步加速器的快速成像时间允许在3到20分钟内完成整个扫描,如表1所示,针对不同的光学布置。每次扫描都会产生1024个图像,这些图像是使用网络软件[8]在ALS使用过滤反投影法重建的。重建完成后,使用商业软件包Avizo对三维图像进行可视化和分析。

表1.不同相机和镜头的分辨率、视场(FOV)和成像时间摘要。突出显示的行用于本次调查,以便在3分钟内成像整个16x16毫米芯片。

同步X射线CT成像的SIP封装

要成像的微电子组件是一个3d SIP组件,尺寸为16x16 mm,厚度约为3 mm。如图11所示,将包装放置在水平方向的光束线上,这样可以在一次扫描中对整个封装进行成像。SIP封装(图11)由连接到FPGA基板的FPGA硅芯片组成,第一级互连(FLI)焊点直径约为100mu;m;中层互连(MLI)焊点直径约为350mu;m,将FPGA基板连接到SIP基板;第二级互连(SLI)焊球直径约为在SIP基板背面约650mu;m。

图11.同步加速器CT研究中使用的SIP封装的示意图。16x16 mm的封装相对

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[608939],资料为PDF文档或Word文档,PDF文档可免费转换为Word

您可能感兴趣的文章

- 饮用水微生物群:一个全面的时空研究,以监测巴黎供水系统的水质外文翻译资料

- 步进电机控制和摩擦模型对复杂机械系统精确定位的影响外文翻译资料

- 具有温湿度控制的开式阴极PEM燃料电池性能的提升外文翻译资料

- 警报定时系统对驾驶员行为的影响:调查驾驶员信任的差异以及根据警报定时对警报的响应外文翻译资料

- 门禁系统的零知识认证解决方案外文翻译资料

- 车辆废气及室外环境中悬浮微粒中有机磷的含量—-个案研究外文翻译资料

- ZigBee协议对城市风力涡轮机的无线监控: 支持应用软件和传感器模块外文翻译资料

- ZigBee系统在医疗保健中提供位置信息和传感器数据传输的方案外文翻译资料

- 基于PLC的模糊控制器在污水处理系统中的应用外文翻译资料

- 光伏并联最大功率点跟踪系统独立应用程序外文翻译资料